Grundlagen der Digitaltechnik (3V1Ü) (früher: Entwurf digitaler Schaltungen)

(C. Giesemann)

Die Vorlesung führt in den rechnergestützten Entwurf digitaler Schaltungen ein. Behandelt werden das logische und das Zeitverhalten, Automaten und andere Verhaltensmodelle für sequentielle Schaltungen, Rechenwerke, Simulation, Synthese und Logikoptimierung. Im begleitenden Praktikum digitaler Schaltungsentwurf I werden digitale Schaltungen entworfen, simuliert, in programmierbare Logikschaltkreise programmiert und ausprobiert.

Überblick

Inhalt der Lehrveranstaltung

- Zwei einführende Beispiele: einen Entwurf mit Standardschaltkreisen und einen VHDL-Entwurf für FPGAs.

- Simulation: VHDL, ereignisgesteuerte Simulation, Laufzeittoleranz, ...

- Synthese und Schaltungsoptimierung: synthesegerechte Beschreibung, asynchrone Eingabe, KV-Diagramm, ROBDD.

- Rechenwerke und Operationsabläufe: Addierer, ..., Automaten, serielle Schnittstelle, ...

- Vom Transistor zur Schaltung: MOS-Transistoren, Gatter, Layout, Verzögerung, ...

- Rechner: CORDIC, Minimalprozessor, Pipeline.

Zielgruppe: Bachelor Informatik und weitere

Credits: (ECTS): 6

Foliensätze, Handouts für den Ausdruck und Beispielprogramme

Foliensätze [F], Handouts für den Ausdruck [H] und Beispielprogramme [P]

- [F1] [H1] Einführung

- Einleitung: Einleitung, Aufbau, Überblick.

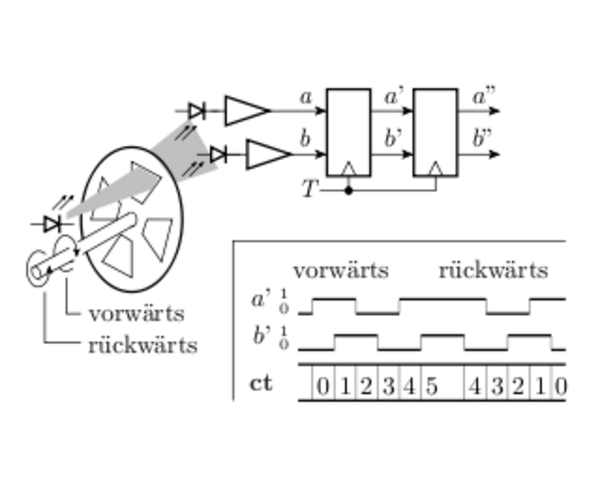

- Standardschaltkreise: Entwurf eines Zählers, Test der Zählfunktion, Zustandsregister, Leiterplattenentwurf.

- VHDL + FPGA: Einfache Gatterschaltung, Zähler und Ampelsteuerung, Simulation.

- [F2] [H2] [P2] Simulation

- Einführung in VHDL: Hallo Welt, Signale, Datentypen, imperative Modelle, ereignisgesteuerte Simulation.

- Strukturbeschreibung: Schnittstellen, Instanziierung und Verbinden von Teilschaltungen, Testrahmen.

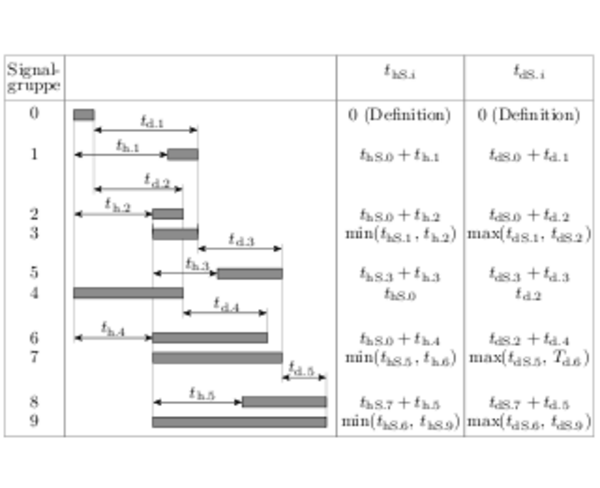

- Laufzeittoleranz: Glitches, Simulation von Zeittoleranzen, Laufzeitanalyse.

- Speicher: Latches, Register, Verarbeitung + Abtastung, Register-Transfer-Funktionen, adressierbare Speicher.

- [F3] [H3] Synthese und Schaltungsoptimierung

- Synthese: Verarbeitungsfunktionen, Register-Transfer-Funktionen, typische Beschreibungsfehler, Constraints.

- Asynchrone Eingabe: Abtastung, Initialisierung, Entprellen, asynchrone Schnittstellen mit und ohne Übertragung des Sendertaktes.

- Schaltungsoptimierung: Energieverbrauch, Schaltungsumformung, KV-Diagramm, Verfahren von Quine und McCluskey, reduziertes geordnetes binäres Entscheidungsdiagramm (ROBDD).

- [F4] [H4] [P4] Rechenwerke und Operationsabläufe

- Rechenwerke: Addierer, Subtrahierer, Zähler etc. Multiplizierer, Komparatoren, Block-Shifter.

- Automaten: Entwurf mit KV-Diagrammen, Beschreibung in VHDL, redundante Zustände, Spezifikation und Entwurf.

- Operationsabläufe: serielle Schnittstelle, serieller Addierer, Dividierer.

- [F5] [H5] Vom Transistor zur Logikschaltung

- Gatterentwurf: MOS-Transistoren als Schalter, FCMOS-Gatter, deaktivierbare Treiber, Transfergatter und Multiplexer, geometrischer Entwurf.

- Signalverzögerung: Inverter, Logikgatter, Puffer.

- Latches und Register.

- Blockspeicher: SRAM, Mehrport- und Assoziativspeicher, DRAM, Festwertspeicher.

- Programmierbare Logikschaltkreise.

- Schaltungsentwurf mit FPGAs.

- [F6] [H6] [P6] Rechnerstrukturen

- CORDIC: Algorithmus, Simulation des Algrithmus, Umstellung auf Festkommazahlen, Entwurf als Rechenwerk, Testrahmen.

- MiPro (Minimalprozessor): Funktion und Befehlssatz, Assembler und Disassembler, Prozessorzustand, Simulationsmodell, Testrahmen, Testbeispiele.

- RISC-Prozessor: Pipeline-Verarbeitung, Simulationsmodell, Testbeispiele.

Große Übungen und Laborübungen

- Große Übung 1: Logik und Signalverläufe [G1] 21.04.2022 Hörsaal

- Laborübung 1: Schaltungsentwurf mit Standardschaltkreisen [L1] 28.04.2022 Labor, 10:15 bis 11:45, wenn nötig auch 8:30 bis 10:00

- Laborübung 2: Schaltungsentwurf in VHDL mit FPGA [L2] 05.05.2022 Labor, 10:15 bis 11:45, wenn nötig auch 8:30 bis 10:00 [EDS_GU2.zip]

- Große Übung 2: Signaldarstellung, Signalverläufe, Strukturbeschreibung [G2] 12.05.2022 Hörsaal

- Große Übung 3: Zeittoleranzen, Abtastprozess, Register-Transfer-Funktion, Synthese [G3] 19.05.2022 Hörsaal

- Große Übung 4: Signalflussplan, Zwischenabtastung, Asynchrone Übertragung [G4] 02.06.2022 Hörsaal

- Große Übung 5: Register, Sythesefähige Prozesse [G5] 16.06.2022 Hörsaal

- Große Übung 6: Schaltungsumformung, KV, Quine/McCluskey, OBDD [G6] 23.06.2022 Hörsaal

- Große Übung 7: Automaten [G7] 30.06.2022 Hörsaal

- Große Übung 8: FCMOS [G8] 07.07.2022 Hörsaal

- Laborübung 3: Test einer UART [L3] [uart.zip] [USB-LOGI-500] 14.07.2022 Labor, 10:15 bis 11:45, wenn nötig auch 8:30 bis 10:00

- Große Übung 9: CMOS, Transfergatter, Register [G9] 21.07.2022 Hörsaal

- Große Übung Klausur: Rechnen einer Klausur 28.07.2022 Hörsaal

Hausaufgaben

Die Lösungen sind als PDF mit Dateinamen

EDS_<anr>_<name>_<matr>_<opt>.pdf

(<anr> – Aufgabenummer, <name> – ihr Name, <matr> – ihre Matrikel-Nummer, <opt> – optionales Kürzel bei mehreren Dateien) bis zu den in der Ablauftabelle angegebenen Tagen per E-Mail an

ha-eds(at)in.tu-clausthal.de

zu schicken. Sie werden korrigiert und zurückgesendet. Bei den Hausübungen ist keine Gruppenarbeit zulässig.

- [HA1] , Abgabe 29.04.2022

- [HA2] , Abgabe 13.05.2022 (Bearbeitungszeit 2 Wochen), Programmdateien: [PHA2],

- [HA3] , Abgabe 20.05.2022, Programmdateien: [PHA3]

- [HA4] , Abgabe 27.05.2022, Programmdateien: [PHA4]

- keine Abgaben am 02.06.2022 und 09.06.2022

- [HA5] , Abgabe 17.06.2022

- [HA6] , Abgabe 24.06.2022

- [HA7] , Abgabe 01.07.2022

- [HA8] , Abgabe 08.07.2022 bis zur Laborübung!, Programmdateien: [PHA8]

- [HA9] , Abgabe 15.07.2022

ghdl unter Debian 9.8 und unter Ubuntu 18.04.2

Man kann ghdl aus den debian repos gcc-6-base in der version 6.3.0 herunterladen und installieren. Quellen:

- packages.debian.org/stretch/amd64/gcc-6-base/download

- packages.debian.org/stretch/amd64/libgnat-6/download

Zur Vermeidung von Konflikten durch das gcc-Downgrade von Version 6.5 auf Version 6.3 empfiehlt sich die Installation in einer virtuellen Maschine.

Ergebnisse:

Den Leistungsnachweis für die Hausübungen gibt es ab insgesamt 50 Übungspunkte. Ab 100 HP (Hausübungspunkten) gibt es 2 BP (Bonuspunkte), sonst ab 88 HP gibt es 1.5 BP, sonst ab 76 HP gibt es 1 BP und sonst ab 64 HP gibt es 0.5 BP für die Prüfungsklausur.

(LNE - Leistungsnachweis erteilt, BP - Bonuspunkte für die Prüfungsklausur)

| Code | Ü1 | Ü2 | Ü3 | Ü4 | Ü5 | Ü6 | Ü7 | Ü8 | Ü9 | Sum | LNE | BP |

|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 39468G | 10 | 13 | 13 | 11 | 14 | |||||||

| 47095B | 9,5 | 7 | 13,5 | 11 | - | |||||||

| 50863G | 8,5 | 11 | 11,5 | 8,5 | 11,5 | |||||||

| 50728C | 2,5 | - | - | - | - | |||||||

| 51620G | 1,5 | - | 6 | 10 | 8 | |||||||

| 51723A | 2 | 5,5 | - | - | - | |||||||

| 51154G | 9,5 | 13 | 14 | 11 | 9 | |||||||

| 52073K | 10 | 12,5 | 13,5 | 10 | 11 | |||||||

| 52356B | 9 | 13 | 7 | 11,5 | 8,5 | |||||||

| 52386A | 3,5 | 3 | - | - | - | |||||||

| 52917A | 5 | 12,5 | 14 | - | 9 | |||||||

| 53550E | 9,5 | 11,5 | 1 | 10 | 8 | |||||||

| 53892F | 4 | - | - | - | - | |||||||

| 53293C | 9,5 | - | 13 | 10 | 8 | |||||||

| 53823D | 10 | 12 | 7 | 12 | 12,5 | |||||||

| 53913H | 7 | 11,5 | 13,5 | 9 | 12 | |||||||

| 53005K | 5,5 | 13 | 14 | 10 | 10 | |||||||

| 53456B | 3 | 12,5 | 13 | 9,5 | 8,5 | |||||||

| 53546F | 3 | - | - | - | - | |||||||

| 53656F | 7 | 12,5 | - | 3,5 | 7 | |||||||

| 53696H | 9,5 | 10,5 | 8 | 7 | 8,5 | |||||||

| 53796E | 7 | 7 | 12,5 | 12 | 11,5 | |||||||

| 53896B | 10 | 14 | 13 | 3 | 8 | |||||||

| 53986F | 7 | - | 13,5 | 9,5 | - | |||||||

| 53287F | 3,5 | 5,5 | - | - | - | |||||||

| 53068E | 7 | 13 | 13,5 | 10 | 12 | |||||||

| 54011K | 5,5 | - | - | - | - | |||||||

| 54101D | 10 | 7 | 13 | 11 | 11 | |||||||

| 54272A | 6 | 6 | 6 | 5 | 8,5 | |||||||

| 54482H | 4,5 | - | - | - | - | |||||||

| 54532K | 6 | 13 | 14 | 9 | 11 | |||||||

| 54732D | 6 | 7,5 | 8,5 | 8,5 | ||||||||

| 54862K | 7 | 2 | - | - | - | |||||||

| 54003E | 9,5 | 14 | 13 | 11 | 13,5 | |||||||

| 54153G | 14 | - | - | |||||||||

| 54313I | 7,5 | 13 | 3 | - | 7,5 | |||||||

| 51342I | 4,5 | 4 | 4 | 9 | 7 | |||||||

| 54513C | 7 | 0 | - | - | - |

Literatur

- G. Kemnitz: Technische Informatik Band 2: Entwurf digitaler Schaltungen. Springer. 2011.

- P. J. Ashenden: Designer's Guide to VHDL. Morgan Kaufmann Publishers. 2008.

- J. Reichert, B. Schwarz: VHDL-Synthese: Entwurf digitaler Schaltungen und Systeme. Oldenbourg. 2009

- VHDL-Books Nur im Uni-Netz verfügbar, extern ist [VPN] nötig.

Aktuelles

Die Prüfungsklausur zu Grundlagen der Digitaltechnik wird im September/Oktober 2022 stattfinden. Genauere Details folgen zu gegebener Zeit. Erlaubte Hilfsmittel für die Prüfung sind eigene Ausarbeitungen und Taschenrechner. Zu den eigenen Ausarbeitungen zählen Mitschriften, die Foliensätze bzw. Handouts mit eigenen Kommentaren, die zurückgegebenen korrigierten Hausübungen, selbst angefertigte schriftliche Prüfungsvorbereitungen und Bücher mit Lesezeichen und Notizzetteln. Kommunikation mit anderen Personen ist während der Prüfung untersagt.