EDS - SS15

(G. Kemnitz, C. Giesemann)

Die Vorlesung führt in den rechnergestützten Entwurf digitaler Schaltungen ein. Behandelt werden das logische und das Zeitverhalten, Automaten und andere Verhaltensmodelle für sequentielle Schaltungen, Rechenwerke, Simulation, Synthese und Logikoptimierung. Im begleitenden Praktikum digitaler Schaltungsentwurf I werden digitale Schaltungen entworfen, simuliert, in programmierbare Logikschaltkreise programmiert und ausprobiert.

Inhalt der Lehrveranstaltung

- Zwei einführende Beispiele: einen Entwurf mit Standardschaltkreisen und einen VHDL-Entwurf für FPGAs.

- Handwerkzeug des digitalen Schaltungsentwurfs: Beschreibung für die Simulation und Synthese (VHDL), Optimierung (KV-Diagramme), Rechenwerke, Automaten, Operationsabläufe, Zeitverhalten und asynchrone Datenübergabe.

- Vom Transistor zur Schaltung: Gatter, Speicherzellen, Blockspeicher, programmierbare Logikschaltungen.

- Komplexe Entwürfe: serielle Schnittstelle, Cordic-Rechenwerk und Spezialrechner für FIR-Filter.

Zielgruppe: Bachelor Informatik, Bachelor Technische Informatik

Credits: (ECTS): 6

Foliensätze

- [F1: Einführung]

- Standardschaltkreise: Beispielentwurf, Test, Schaltungen mit Registern, Leiterplattenentwurf.

- VHDL + FPGA: Einfache Gatterschaltung, Zähler und Ampelsteuerung, Simulation.

- [F2: Handwerkszeug Teil 1]

- Simulation: VHDL, Signale, Datentypen, Imperative Modelle, Ereignisgesteuerte Simulation, Strukturbeschreibung, Speicher.

- Synthese: Verarbeitungsfunktionen, Register-Transfer-Funktion, Typische Beschreibungsfehler.

- Optimierung: Optimierungsziele, Logikvereinfachung, KV-Diagramme, Quine und McCluskey, Vereinfachung mit BDDs.

- Rechenwerke: Addierer, Subtrahierer, Zähler etc., Multiplizierer, Komparatoren, Block-Shifter.

- [F3: Handwerkszeug Teil 2]

- Automaten: Modellierung und Klassifikation, Automat als Schaltung, Entwurf mit KV-Diagrammen, Beschreibung in VHDL, Redundante Zustände, Beispiel Zahlenschloss.

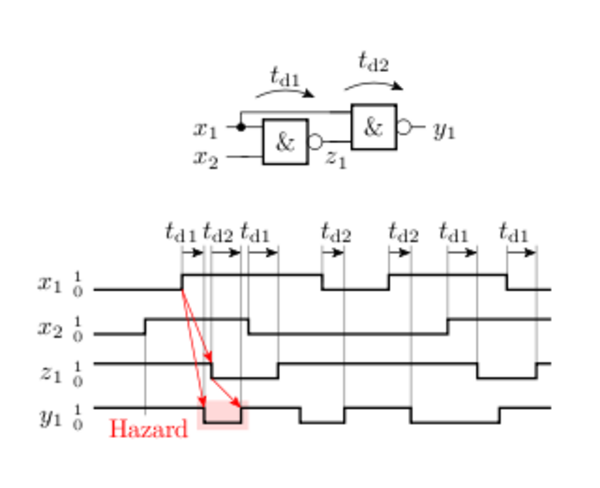

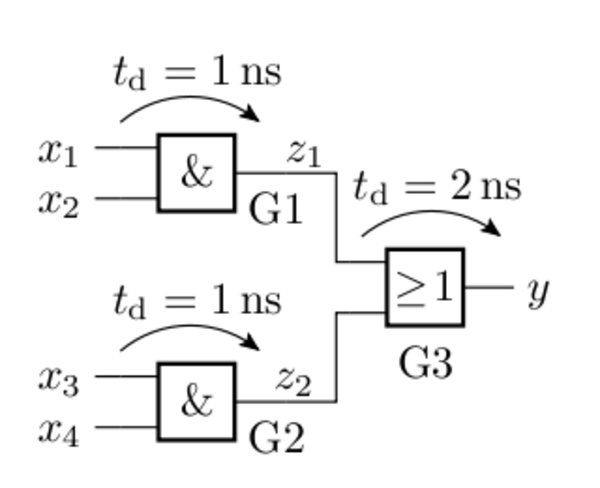

- Zeitverhalten: Halte- und Verzögerungszeiten, Laufzeitanalyse, Speichervor- und Nachhaltezeiten, Register-Transfer-Funktionen, Constraints.

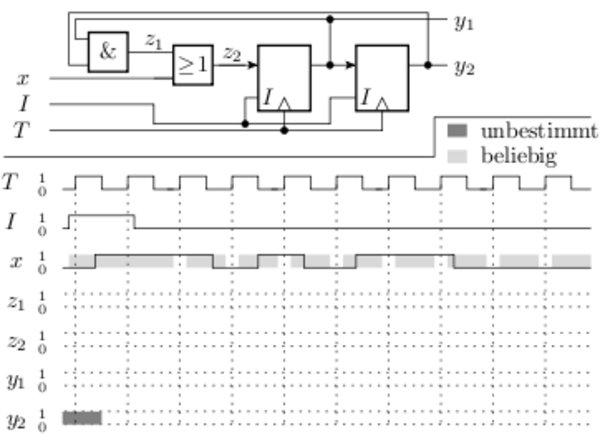

- Asynchrone Eingabe: Abtastung, Entprellen, Asynchrone Initialisierung, Eingabesynchronisation.

- [F4: Vom Transistor zum Logikbaustein]

- Gatterentwurf: MOS-Transistoren als Schalter, FCMOS-Gatter, Deaktivierbare Treiber, Transfergatter und Multiplexer, Geometrischer Entwurf.

- Signalverzögerung: Verzögerung eines Inverters, Parameterabschätzung, Gatterverzögerung, Gepufferte CMOS.

- Speicher: Speicherzellen, Latches und Register, Taktversorgung.

- Blockspeicher: SRAM, Mehrport- und Assoziativspeicher, DRAM, Festwertspeicher.

- Programmierbare Logikschaltkreise.

- [F5: Komplexe Entwürfe]

- VHDL-2: Eigene Datentypen, Funktionen, Testein- und Testausgabe, Schrittfunktionen.

- UART: Sender, Testrahmen Empfänger, Synthesebeschreibung.

- CORDIC: Algorithmus, Erstes Simulationsmodell, Festkommazahlen, Algorithmus weiter optimieren.

- FIR-Filter: Pipeline und Speicherengpass, FIR-Filter mit Blockspeichern, Der Weg zum ersten Simulationsmodell, Zahlendarstellung durch Bitvektoren, Ein- und Ausgabe über Signale, Schrittkettenbeschreibung.

Große Übung

- [G1] Labor, 16.04.2015 / 20.04.2015

- [G2] Labor, 23.04.2015 / 27.04.2015, [Dateien zu Übung 2]

- [G3] Labor, 07.05.2015 / 11.05.2015, [Dateien zu Übung 3]

- [G4] Hörsaal, 04.06.2015

- [G5] Hörsaal, 18.06.2015

- [G6] Labor, 09.07.2015 / 13.07.2015

- [G7] Hörsaal, 16.07.2015

- [Klausur SS2014] Hörsaal, 23.07.2015

Hausübungen

Die Abgabe von Gruppenarbeiten sind nicht zulässig. Den Leistungsnachweis für die Hausübungen gibt es ab insgesamt 50% der Übungspunkte.

HA1 - Abgabe: verlängert bis 27.04.2015

HA1 - Abgabe: verlängert bis 27.04.2015 HA2 - Abgabe: 30.04.2015

HA2 - Abgabe: 30.04.2015 HA3 - Abgabe: verlängert bis 11.05.2015

HA3 - Abgabe: verlängert bis 11.05.2015 HA4 - Abgabe: 13.05.2015

HA4 - Abgabe: 13.05.2015 HA5 - Abgabe: 21.05.2015

HA5 - Abgabe: 21.05.2015 HA6 - Abgabe: 04.06.2015

HA6 - Abgabe: 04.06.2015 HA7 - Abgabe: 11.06.2015

HA7 - Abgabe: 11.06.2015 HA8 - Abgabe: 18.06.2015

HA8 - Abgabe: 18.06.2015 HA9 - Abgabe: 25.06.2015

HA9 - Abgabe: 25.06.2015 HA10 - Abgabe: 02.07.2015

HA10 - Abgabe: 02.07.2015 HA11 - Abgabe: verlängert bis 13.07.2015 (letzte Hausübung)

HA11 - Abgabe: verlängert bis 13.07.2015 (letzte Hausübung)

Ergebnisse

| Matrn | Ü1 | Ü2 | Ü3 | Ü4 | Ü5 | Ü6 | Ü7 | Ü8 | Ü9 | Ü10 | Ü11 | Summe | ZP |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| (10) | (12) | (10) | (12) | (12) | (12) | (11) | (10) | (10) | (10) | (10) | 119 | ||

| 439844 | 7 | 10 | 6,5 | 9,5 | 9,5 | 11 | 3,5 | 3,5 | 7 | 8,5 | 76 | 2,5 | |

| 423865 | 6,5 | 8,5 | 8 | 11 | 10 | 8 | 6,5 | 4 | 62,5 | 2,0 | |||

| 432232 | 6 | 10,5 | 9,5 | 9 | 6 | 9,5 | 5,5 | 10 | 8 | 10 | 4,5 | 88,5 | 3,0 |

| 447344 | 7 | 10,5 | 6,5 | 10,5 | 8 | 7,5 | 3 | 53 | 2,0 | ||||

| 442514 | 7 | 9,5 | 8,5 | 10 | 6 | 11,5 | 9,5 | 10 | 6,5 | 8 | 10 | 96,5 | 3,0 |

| 449009 | 10 | 12 | 10 | 11 | 10 | 10,5 | 9 | 7 | 9 | 10 | 10 | 108,5 | 3,5 |

| 304120 | 10 | 11 | 10 | 11 | 10 | 12 | 8 | 7 | 6 | 10 | 9 | 104 | 3,5 |

| 412991 | 8,5 | 7 | 9,5 | 8 | 11,5 | 2 | 9,5 | 56 | 2,0 | ||||

| 380438 | 6 | 9,5 | 8,5 | 4 | 4 | 12 | 5,5 | 7 | 7 | 6 | 69,5 | 2,5 | |

| 449573 | 6 | 10 | 10 | 9 | 9,5 | 8,5 | 6 | 8 | 7 | 8 | 9 | 91 | 3,0 |

| 447447 | 8,5 | 11 | 8 | 8 | 10 | 10 | 11 | 6 | 5 | 10 | 10 | 97,5 | 3,0 |

| 444011 | 6 | 7,5 | 9,5 | 10,5 | 10 | 6 | 7,5 | 4 | 5 | 66 | 2,0 | ||

| 403627 | 8 | 10,5 | 9,5 | 10,5 | 10,5 | 2 | 8,5 | 3 | 62,5 | 2,0 | |||

| 420013 | 10 | 12 | 9 | 10 | 11 | 11,5 | 11 | 10 | 10 | 94,5 | 3,0 | ||

| 442727 | 5 | 9,5 | 8 | 10,5 | 10,5 | 11,5 | 7,5 | 8 | 7 | 9,5 | 3 | 90 | 3,0 |

| 441379 | 10 | 9,5 | 8 | 10 | 9,5 | 12 | 4,5 | 8 | 10 | 9 | 90,5 | 3,0 | |

| 414869 | 6 | 6 | * | ||||||||||

| 459116 | 3 | 9 | 7,5 | 10 | 4,5 | 10 | 7,5 | 6 | 4 | 7,5 | 3,5 | 72,5 | 2,5 |

| 428585 | 2,5 | 7,5 | 5,5 | 5,5 | 1,5 | 22,5 | 1* | ||||||

| 450100 | 10 | 12 | 9 | 11 | 4 | 10,5 | 2 | 7 | 10 | 10 | 85,5 | 3,0 | |

| 423607 | 6 | 9,5 | 3 | 10,5 | 5 | 10 | 7 | 2,5 | 7 | 7,5 | 68 | 2,5 | |

| 432713 | 8 | 10 | 6,5 | 0,5 | 3 | 1 | 29 | 1* | |||||

| 430704 | 5,5 | 10,5 | 9,5 | 9 | 6 | 9,5 | 4,5 | 10 | 8 | 10 | 4,5 | 87 | 3,0 |

| 402592 | 6 | 9 | 7,5 | 9,5 | 2 | 10,5 | 3,5 | 5 | 4,5 | 3,5 | 61 | 2,0 | |

| 309929 | 7 | 5,5 | 9,5 | 9 | 5 | 10 | 7 | 53 | 2,0 | ||||

| 433453 | 8 | 9 | 9,5 | 10 | 5 | 11 | 4 | 0,5 | 57 | 2,0 | |||

| 447337 | 7 | 8,5 | 9,5 | 10,5 | 6 | 10,5 | 5 | 6,5 | 6 | 7 | 8 | 84 | 3,0 |

| 430845 | 8 | 9,5 | 8 | 10,5 | 5 | 11 | 4 | 0,5 | 56,5 | 2,0 | |||

| 429438 | 6 | 10,5 | 9,5 | 9 | 6,5 | 9,5 | 4,5 | 10 | 8 | 10 | 4,5 | 88 | 3,0 |

| 431293 | 8,5 | 6,5 | 8,5 | 9 | 7 | 11 | 2 | 6 | 5,5 | 6 | 70 | 2,5 | |

| 432438 | 8,5 | 10 | 7 | 7 | 2 | 8 | 5,5 | 48 | 1,5* | ||||

| 443560 | 5 | 7 | 6 | 10,5 | 8 | 11 | 8 | 4 | 4,5 | 4,5 | 68,5 | 2,5 | |

| 430522 | 6 | 10,5 | 9,5 | 9 | 5 | 9,5 | 5,5 | 10 | 8 | 10 | 4,5 | 87,5 | 3,0 |

| 416706 | 8 | 10,5 | 8,5 | 9 | 6 | 3 | 7 | 5,5 | 4,5 | 62 | 2,0 | ||

| 421351 | 9 | 7 | 8,5 | 10 | 6,5 | 41 | 1,5* | ||||||

| 434492 | 9 | 6 | 9,5 | 9,5 | 10,5 | 12 | 10 | 6 | 3,5 | 8 | 9 | 93 | 3,0 |

| 432658 | 9 | 10,5 | 3,5 | 11 | 3 | 6 | 43 | 1,5* | |||||

| 447698 | 7 | 9,5 | 6,5 | 9,5 | 8 | 7,5 | 3,5 | 3 | 4 | 58,5 | 2,0 | ||

| 448352 | 1,5 | 10 | 11 | 6 | 8 | 7,5 | 8 | 8 | 10 | 9 | 79 | 2,5 | |

| 443405 | 6 | 9 | 9,5 | 8,5 | 10 | 11 | 4 | 6 | 7 | 8 | 79 | 2,5 | |

| 445029 | 9,5 | 11 | 9,5 | 9,5 | 9 | 11 | 7 | 8 | 7 | 9 | 10 | 100,5 | 3,5 |

| 444657 | 8 | 7,5 | 7,5 | 10,5 | 5 | 11 | 2 | 8 | 9 | 8,5 | 77 | 2,5 | |

| 444190 | 6 | 6,5 | 7,5 | 6,5 | 11 | 11,5 | 6 | 8 | 3 | 7,5 | 73,5 | 2,5 | |

| 419912 | 8,5 | 7 | 9 | 9,5 | 11 | 2 | 10 | 5 | 62 | 2,5 | |||

| 449212 | 7 | 7,5 | 7,5 | 11 | 6 | 11 | 2,5 | 8 | 9 | 8,5 | 78 | 2,5 |

* Leistungsnachweis für die Hausübungen wird nicht erteilt.

Dokumente

Literatur

- G. Kemnitz: Technische Informatik Band 2: Entwurf digitaler Schaltungen. Springer. 2011.

- P. J. Ashenden: Designer's Guide to VHDL. Morgan Kaufmann Publishers. 2008.

- J. Reichert, B. Schwarz: VHDL-Synthese: Entwurf digitaler Schaltungen und Systeme. Oldenbourg. 2009

- VHDL-Books

Aktuelles

Die Prüfung findet als Klausur am Di., den 06.10.2015 von 9:30 bis 11:00 Uhr voraussichtlich im HA im Institut für Mathematik statt. Erlaubte Hilfsmittel für die Prüfung sind eigene Ausarbeitungen und Taschenrechner. Zu den eigenen Ausarbeitungen zählen Mitschriften, die ausgeteilten Foliensätze mit eigenen Kommentaren, die zurückgegebenen korrigierten Hausübungen, selbst angefertigte schriftliche Prüfungsvorbereitungen und Bücher mit Lesezeichen und Notizzetteln. Handys sind während der Prüfung auszuschalten. Laptops und andere elektronische Hilfsmittel sind nicht zugelassen.