EDS - SS14

(G. Kemnitz, C. Giesemann)

Die Vorlesung führt in den rechnergestützten Entwurf digitaler Schaltungen ein. Behandelt werden das logische und das Zeitverhalten, Automaten und andere Verhaltensmodelle für sequentielle Schaltungen, Rechenwerke, Simulation, Synthese und Logikoptimierung. Im begleitenden Praktikum digitaler Schaltungsentwurf I werden digitale Schaltungen entworfen, simuliert, in programmierbare Logikschaltkreise programmiert und ausprobiert.

Inhalt der Lehrveranstaltung

- Zwei einführende Beispiele: einen Entwurf mit Standardschaltkreisen und einen VHDL-Entwurf für FPGAs.

- Handwerkzeug des digitalen Schaltungsentwurfs: Beschreibung für die Simulation und Synthese (VHDL), Optimierung (KV-Diagramme), Rechenwerke, Automaten, Operationsabläufe, Zeitverhalten und asynchrone Datenübergabe.

- Vom Transistor zur Schaltung: Gatter, Speicherzellen, Blockspeicher, programmierbare Logikschaltungen.

- Komplexe Entwürfe: serielle Schnittstelle, Cordic-Rechenwerk und Spezialrechner für FIR-Filter.

Zielgruppe: Bachelor Informatik, Bachelor Technische Informatik

Credits: (ECTS): 6

Foliensätze

- [F1: Einführung]

- Standardschaltkreise: Beispielentwurf, Test, Schaltungen mit Registern, Leiterplattenentwurf.

- VHDL + FPGA: Einfache Gatterschaltung, Zähler und Ampelsteuerung, Simulation.

- [F2: Handwerkszeug Teil 1]

- Simulation: VHDL, Signale, Datentypen, Imperative Modelle, Ereignisgesteuerte Simulation, Strukturbeschreibung, Speicher.

- Synthese: Verarbeitungsfunktionen, Register-Transfer-Funktion, Typische Beschreibungsfehler.

- Optimierung: Optimierungsziele, Logikvereinfachung, KV-Diagramme, Quine und McCluskey, Vereinfachung mit BDDs.

- Rechenwerke: Addierer, Subtrahierer, Zähler etc., Multiplizierer, Komparatoren, Block-Shifter.

- [F3: Handwerkszeug Teil 2]

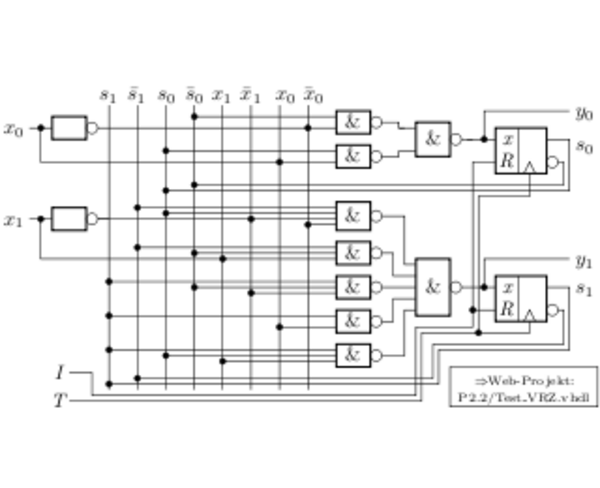

- Automaten: Modellierung und Klassifikation, Automat als Schaltung, Entwurf mit KV-Diagrammen, Beschreibung in VHDL, Redundante Zustände, Beispiel Zahlenschloss.

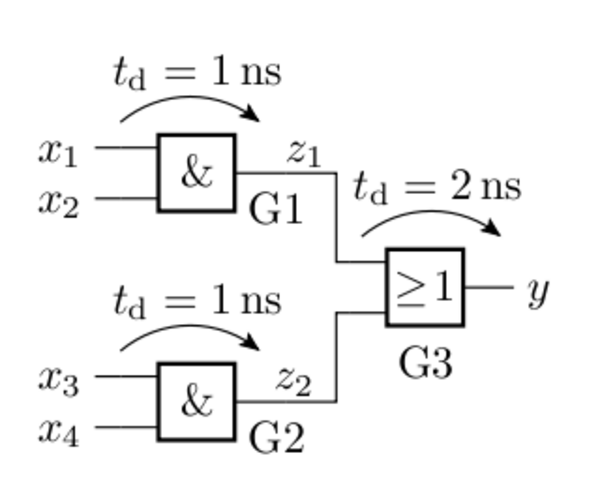

- Zeitverhalten: Halte- und Verzögerungszeiten, Laufzeitanalyse, Speichervor- und Nachhaltezeiten, Register-Transfer-Funktionen, Constraints.

- Asynchrone Eingabe: Abtastung, Entprellen, Asynchrone Initialisierung, Eingabesynchronisation.

- [F4: Vom Transistor zum Logikbaustein]

- Gatterentwurf: MOS-Transistoren als Schalter, FCMOS-Gatter, Deaktivierbare Treiber, Transfergatter und Multiplexer, Geometrischer Entwurf.

- Signalverzögerung: Verzögerung eines Inverters, Parameterabschätzung, Gatterverzögerung, Gepufferte CMOS.

- Speicher: Speicherzellen, Latches und Register, Taktversorgung.

- Blockspeicher: SRAM, Mehrport- und Assoziativspeicher, DRAM, Festwertspeicher.

- Programmierbare Logikschaltkreise.

- [F5: Komplexe Entwürfe]

- VHDL-2: Eigene Datentypen, Funktionen, Testein- und Testausgabe, Schrittfunktionen.

- UART: Sender, Testrahmen Empfänger, Synthesebeschreibung.

- CORDIC: Algorithmus, Erstes Simulationsmodell, Festkommazahlen, Algorithmus weiter optimieren.

- FIR-Filter: Pipeline und Speicherengpass, FIR-Filter mit Blockspeichern, Der Weg zum ersten Simulationsmodell, Zahlendarstellung durch Bitvektoren, Ein- und Ausgabe über Signale, Schrittkettenbeschreibung.

Laborübungen und Große Übungen

- 17. KW, 1. Laborübung [Schaltungsentwurf mit Standardschaltkreisen] , Gruppe 1 Di. 22.04. 10-12, Gruppe 2 Do. 24.04. 10-12

- 19. KW, 2. Laborübung [Schaltungsentwurf in VHDL für FPGAs] ( [EDS-Ue2.zip] ), Gruppe 1 Di. 06.05. 10-12, Gruppe 2 Do. 08.05. 10-12

- 21. KW, [1. Große Übung] , alle gemeinsam Do. 22.05. 10-12

- 25. KW, 3. Laborübung (Entwurf Zahlenschloss), Gruppe 1 Di. 17.06. 10-12, Gruppe 2 Do. 19.06. 10-12

- 27. KW, [2. Große Übung] , alle gemeinsam Do. 03.07. 10-12

- 29. KW, [3. Große Übung] , alle gemeinsam Do. 17.07. 10-12

- 30. KW, 4. Große Übung, Klausurvorbereitung, alle gemeinsam Do. 24.07. 10-12

Hausübungen

Ergebnisse

| Matrn | Ü1 | Ü2 | Ü3 | Ü4 | Ü5 | Ü6 | Ü7 | Ü8 | Ü9 | Ü10 | Ü11 | bestanden |

|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 403191 | 10 | 10 | 11 | 8,5 | 7,5 | 9,5 | 8 | 9 | 9,5 | 7,5 | 7 | ja/4ZP |

| 426181 | nein | |||||||||||

| 440079 | nein | |||||||||||

| 418791 | 9,5 | 9,5 | 8,5 | nein | ||||||||

| 430821 | nein | |||||||||||

| 432225 | 5,5 | 10 | 5,5 | 6 | 6 | 8 | 4 | 2,5 | 5 | 5 | ja/2ZP | |

| 405131 | 10 | 11 | 9 | 7,5 | 7 | 9,5 | 5 | 5 | 2,5 | 6,5 | 7 | ja/3ZP |

| 430618 | 5,5 | 10 | 11 | 6 | 7,5 | 4,5 | 6 | 5,5 | 6 | 3,5 | ja/2.5ZP | |

| 441616 | nein | |||||||||||

| 417996 | 10 | 7,5 | 9 | 9,5 | 10 | 7,5 | 8 | 7 | 8,5 | 9 | ja/3.5ZP | |

| 404068 | 9,5 | 9 | 6,5 | 10,5 | 8 | 9 | 8 | 7,5 | 7,5 | 7 | ja/3.5ZP | |

| 407322 | 10 | 9,5 | 11,5 | 8,5 | 7,5 | 9,5 | 8 | 8,5 | 9,5 | 7,5 | 7 | ja/4ZP |

| 432751 | 9,5 | 10 | 3,5 | 11 | 9,5 | 9,5 | 8 | 9 | 6 | ja/3ZP | ||

| 430467 | nein | |||||||||||

| 407834 | 8,5 | 9 | 6,5 | 8,5 | 5,5 | 9,5 | 10 | 7 | 4 | 6,5 | 6 | ja/3ZP |

| 427285 | nein | |||||||||||

| 438575 | 10 | 10,5 | 11 | 10 | 7 | ja/2ZP | ||||||

| 381453 | nein | |||||||||||

| 404501 | 9,5 | 8,5 | 10 | 10 | 8 | 8,5 | 5,5 | 4,5 | 5,5 | 5,5 | 7 | ja/3.5ZP |

| 432713 | 7 | 6,5 | 6 | 7 | 4,5 | 8 | 5,5 | nein | ||||

| 421430 | 9,5 | 10 | 7 | 7 | 9,5 | nein | ||||||

| 403579 | 10 | 9,5 | 7,5 | 6,5 | nein | |||||||

| 402592 | nein | |||||||||||

| 309929 | 10 | 10 | 9,5 | 10 | 7 | 10 | 8 | 10 | ja/3.5ZP | |||

| 428970 | 6,5 | 9,5 | 4 | 11 | 8 | 9,5 | 8 | 8 | 5,5 | 8 | 8 | ja/3.5ZP |

| 433453 | 5,5 | 10 | 3,5 | 9,5 | 9,5 | 7,5 | 5 | 3 | ja/2ZP | |||

| 407621 | 9,5 | 9,5 | 10,5 | 8,5 | 7,5 | 9,5 | 8 | 8,5 | 9,5 | 7,5 | 6 | ja/4ZP |

| 420556 | 6 | 10 | 11,5 | 8,5 | 8,5 | 9,5 | 3,5 | 10 | 6,5 | 9 | 8,5 | ja/4ZP |

| 419259 | 10 | 9,5 | 9 | 10 | 8,5 | 10 | 8 | 8 | 8 | 9 | 9 | ja/4ZP |

| 407535 | 10 | 8,5 | 9,5 | 8,5 | 8,5 | 9,5 | 8 | 8,5 | 3,5 | 7,5 | 6,5 | ja/4ZP |

| 389688 | nein | |||||||||||

| 430498 | 8,5 | 7,5 | 5,5 | 9,5 | 9,5 | 5 | 5 | 5 | 7,5 | 4,5 | 6 | ja/3ZP |

| 433350 | 7,5 | 10 | 4,5 | 8,5 | 6,5 | 6,5 | 3,5 | 4,5 | 4,5 | ja/2ZP | ||

| 437615 | nein | |||||||||||

| 430845 | 5,5 | 10 | 3,5 | 9,5 | 9,5 | 7,5 | 5 | 3 | ja/2ZP | |||

| 349226 | nein | |||||||||||

| 435149 | nein | |||||||||||

| 429902 | 6,5 | 9 | 6,5 | 10,5 | 10 | 9,5 | 5,5 | 8 | 8 | 6 | 5 | ja/3.5ZP |

| 420642 | 9,5 | 9,5 | 8,5 | 9 | 7 | 9,5 | 8 | 8 | 9 | ja/3ZP | ||

| 402585 | 10 | 11 | 10,5 | 6,5 | 6,5 | 9,5 | 4 | 5 | 2,5 | 8 | 8 | ja/3.5ZP |

| 432438 | 8 | 2 | 8,5 | 6 | 4,5 | nein | ||||||

| 430326 | 7 | 5 | 6 | 9 | 4,5 | 8 | nein | |||||

| 368119 | 5,5 | 9 | 5 | 10 | 8,5 | 10 | 8 | 9 | 5,5 | 9 | ja/3.5ZP | |

| 439820 | 5 | 10 | 10,5 | 9 | 6,5 | 10 | 7,5 | 8 | 6 | 9 | 9,5 | ja/4ZP |

| 432108 | 10 | 10 | 5,5 | 11 | 6 | 9 | 6 | 7,5 | 7 | 5 | 9 | ja/3.5ZP |

| 431413 | 9 | 6,5 | 11 | 6,5 | 7,5 | 6 | 5 | 6,5 | 3,5 | ja/2.5ZP | ||

| 416933 | 5,5 | 10 | 5,5 | 6 | 6,5 | 8 | 4 | 2,5 | 5 | 5 | ja/2.5ZP | |

| 431145 | 7 | 8,5 | 4 | 9 | 4,5 | 8 | 0,5 | 3 | 5,5 | 2,5 | 1,5 | ja/2ZP |

| 409159 | 9,5 | 9,5 | 10,5 | 8 | 7,5 | 9,5 | 8 | 1 | 7,5 | 6 | ja/3ZP | |

| 423511 | 10 | 9,5 | 10,5 | 9,5 | 9,5 | 10 | 7 | 8 | 10 | 9 | 9 | ja/4ZP |

| 426875 | 7 | 9 | 9,5 | 11 | 8,5 | 9,5 | 8,5 | 6 | 7 | 6,5 | 8 | ja/3.5ZP |

| 418241 | 9,5 | 10 | 8 | 7,5 | 7 | 8,5 | 6 | 7 | 9,5 | ja/3ZP | ||

| 418454 | nein | |||||||||||

| 418296 | 9,5 | 9,5 | 5,5 | 9 | 6 | 6,5 | 9,5 | ja/2ZP | ||||

| 429469 | 9,5 | 9,5 | 9 | 8,5 | 6 | 7,5 | ja/2ZP |

Dokumente

Literatur

- G. Kemnitz: Technische Informatik Band 2: Entwurf digitaler Schaltungen. Springer. 2011.

- P. J. Ashenden: Designer's Guide to VHDL. Morgan Kaufmann Publishers. 2008.

- J. Reichert, B. Schwarz: VHDL-Synthese: Entwurf digitaler Schaltungen und Systeme. Oldenbourg. 2009

- VHDL-Books

Prüfungsergebnis der Klausur vom 14.10.14

| Matr.Nr | Klausur- + Zusatzpunkte | Note |

|---|---|---|

| ****** | 11+3,5 | n.b. |

| 402585 | 36+3,5 | 1.0 |

| 403191 | 24,5+4 | 2,7 |

| 405501 | 26,5+3,5 | 2,3 |

| 405131 | 27,5+3 | 2,3 |

| 407322 | 35,5+4 | 1,0 |

| ****** | 24,5+4 | 2,7 |

| 407621 | 31+4 | 1,7 |

| 407834 | 29+3 | 2,0 |

| 409159 | 17+3 | 4,0 |

| 416933 | 24,5+2,5 | 3,0 |

| 417996 | 22,5+3,5 | 3,0 |

| 418241 | 16+3 | n.b. |

| 419259 | 24,5+4 | 2,7 |

| 420556 | 24+4 | 2,7 |

| 420642 | 31+3 | 1,7 |

| 423511 | 25+4 | 2,7 |

| 426875 | 29,5+3,5 | 2,0 |

| 427285 | 24+0 | 3,3 |

| 428970 | 32,5+3,5 | 1,3 |

| 429469 | 15,5+2 | n.b. |

| 429902 | 36,5+3,5 | 1,0 |

| 430498 | 21+3,0 | 3,3 |

| 430618 | 24+2,5 | 3,0 |

| 431145 | 19+2 | 4,0 |

| 431413 | 19+2,5 | 4,0 |

| 432108 | 26,5+3,5 | 2,3 |

| 432225 | 18+2 | 4,0 |

| 432751 | 27,5+3 | 2,3 |

| 433350 | 22+2 | 3,3 |

| 439820 | 30+4 | 1,7 |

Teilerfaktor 30 für Zusatzpunkte