EDS - SS13

(G. Kemnitz, C. Giesemann)

Die Vorlesung führt in den rechnergestützten Entwurf digitaler Schaltungen ein. Behandelt werden das logische und das Zeitverhalten, Automaten und andere Verhaltensmodelle für sequentielle Schaltungen, Rechenwerke, Simulation, Synthese und Logikoptimierung. Im begleitenden Praktikum digitaler Schaltungsentwurf I werden digitale Schaltungen entworfen, simuliert, in programmierbare Logikschaltkreise programmiert und ausprobiert.

Inhalt der Lehrveranstaltung

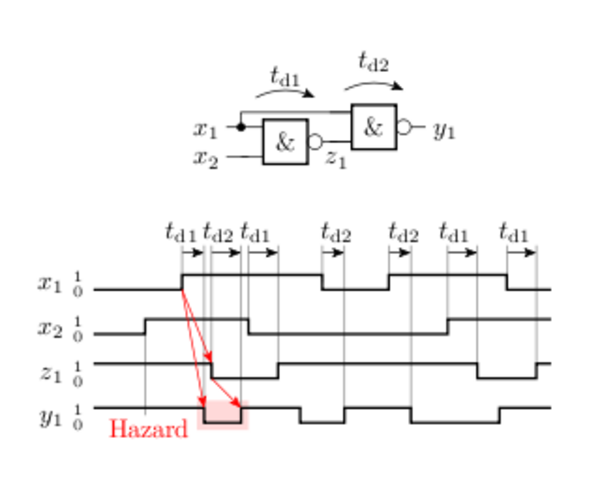

- Modellbildung und Simulation: Funktion, Struktur, Simulation, Laufzeittoleranz, Register, asynchrone Eingabe, sequentielle Schaltungen.

- Vom Transistor zur Schaltung: Gatter, Speicherzellen, Blockspeicher, programmierbare Logikschaltungen.

- Synthese und Logikoptimierung: Register-Transfer-Synthese, Schaltungsvereinfachung, Zahlendarstellung, Rechenwerke.

- Beispielentwürfe

Zielgruppe: Bachelor Informatik, Technische Informatik

Credits: (ECTS): 6

Große Übungen

| Übung | Aufgabenblatt |

|---|---|

| 11.04.13 | [Schaltungen und Signale] |

| 25.04.13 | [Rechnerübung mit dem Simulator ghdl] |

| 16.05.13 | [Laufzeitanalyse, Registerschaltungen] |

| 30.05.13 | [Automaten] |

| 13.06.13 | [Transistorschaltungen] |

| 27.06.13 | [Synthese, Logikoptimierung] |

| 11.07.13 | Prüfungsvorbereitung |

Hausübungen

| VL-Woche | Aufgabenblatt | Punkte | Abgabetermin | Lösung |

|---|---|---|---|---|

| 1 | [EDS-SS12-Ueb1.pdf] | 8 | 11.04.2013 | |

| 2 | [EDS-SS12-Ueb2.pdf] | 12 | 18.04.2013 | |

| 3 | [EDS-SS12-Ueb3.pdf] | 13 | 25.04.2013 | |

| 4 | [EDS-SS12-Ueb4.pdf] | 12 | 02.05.2013 | |

| 5 | [EDS-SS12-Ueb5.pdf] | 12 | 16.05.2013 | |

| 6 | [EDS-SS12-Ueb6.pdf] | 14 | 30.05.2013 | |

| 7 | [EDS-SS12-Ueb7.pdf] | 16 | 06.06.2013 | |

| 8 | [EDS-SS12-Ueb8.pdf] | 14 | 13.06.2013 | |

| 9 | [EDS-SS12-Ueb9.pdf] | 14 | 20.06.2013 |

- Bei Fragen zu ghdl und zur Synthese befinden sich auf der Seite mit den Web-Pojekten getestete Beispielprogramme, die in den Aufgaben jeweils abzuändern sind.

- In den letzten beiden Vorlesungswochen gibt es keine Hausübungen mehr.

Teilnehmer und Ergebnisse

| Matr.-Nr. | A1(8) | A2(12) | A3(14) | A4(12) | A5(10) | A6(14) | A7(16) | A8(14) | A9(14) | Sum | ZP |

|---|---|---|---|---|---|---|---|---|---|---|---|

| 293758 | 8,0 | 11,5 | 13,0 | 8,0 | 7,5 | 13,0 | 11,5 | n.a. | 8,0 | 80,5 | 2,5 |

| 394477 | 7,5 | 11,5 | 10,5 | 11,0 | 9,0 | n.a. | 10,5 | 5,0 | n.a. | 65,0 | 2,0 |

| 395076 | 6,0 | 9,0 | 11,5 | 8,0 | 10,0 | 10,5 | 13,0 | 13,0 | 11,0 | 92,0 | 3,0 |

| 398213 | 8,0 | 11,5 | 11,5 | 10,0 | 12,0 | 12,0 | 15,5 | 10,5 | 11,5 | 102,5 | 3,5 |

| 399953 | 8,0 | 8,5 | 8,5 | 10,5 | 4,5 | 3,0 | 13,5 | 4,0 | 11,0 | 71,5 | 2,5 |

| 400411 | 7,0 | 11,0 | 9,5 | 10,5 | 8,5 | 3,5 | 10,0 | 4,5 | 12,0 | 76,5 | 2,5 |

| 402059 | 8,0 | 11,0 | 12,5 | 10,0 | 10,5 | 7,5 | n.a. | 11,0 | 11,0 | 81,5 | 2,5 |

| 402664 | 7,5 | 11,0 | 10,0 | 9,0 | 11,0 | 9,0 | 8,0 | n.a. | n.a. | 65,5 | 2,0 |

| 403706 | 7,0 | 11,0 | 12,0 | 6,0 | 10,0 | 12,0 | 12,5 | 7,0 | 10,5 | 88,0 | 3,0 |

| 404082 | 7,0 | 10,5 | 12,5 | 9,0 | 10,0 | 10,5 | 13,0 | 12,0 | 10,0 | 94,5 | 3,0 |

| 404099 | 7,5 | 8,5 | 12,5 | n.a. | 9,0 | 8,5 | 10,0 | n.a. | 10,0 | 66,0 | 2,0 |

| 411732 | 8,0 | 10,5 | 11,5 | 11,0 | 11,5 | 11,0 | 16,0 | 10,5 | 11,5 | 101,5 | 3,5 |

| 424897 | 8,0 | 10,5 | 13,0 | 10,0 | 8,5 | 10,0 | 11,0 | n.a. | 12,0 | 83,0 | 3,0 |

| 425403 | 8,0 | 9,0 | 10,0 | 7,5 | n.a. | n.a. | n.a. | n.a. | n.a. | 34,5 | 1,0 |

n.a. -- nicht abgegeben;

2 Zusatzpunkte erhöhen das Prüfungsergebnis um eine Notenstufe, z.B. von 2.0 auf 1.7

Dokumente

Literatur

- G. Kemnitz: Technische Informatik Band 2: Entwurf digitaler Schaltungen. Springer. 2011.

- P. J. Ashenden: Designer's Guide to VHDL. Morgan Kaufmann Publishers. 2008.

- J. Reichert, B. Schwarz: VHDL-Synthese: Entwurf digitaler Schaltungen und Systeme. Oldenbourg. 2009

- VHDL-Books

Aktuelles

Die Prüfungsklausur "Entwurf digitaler Schaltungen" findet am Montag, den 22.07.2013 im Seminarraum B im Institut für Mathematik statt.

Erlaubte Hilfsmittel für die Prüfung sind eigene Ausarbeitungen und Taschenrechner. Zu den eigenen Ausarbeitungen zählen Mitschriften, die ausgeteilten Foliensätze mit eigenen Kommentaren, die zurückgegebenen korrigierten Hausübungen und selbst angefertigte schriftliche Prüfungsvorbereitungen. Laptops, Handys, Bücher und fremde Ausarbeitungen sind nicht zugelassen.

Organisation

Die Veranstaltung hat einen Gesamtstundenumfang von 3V+1Ü. Am Mittwoch ist immer Vorlesung und Donnerstag findet alle zwei Wochen eine Übung statt. Es gibt jede Woche Hausübungen. Abgegebene Hausübungen werden korrigiert zurückgeben. Die erreichten Punkte fließen in Form von Bonuspunkten in die Prüfungsnote mit ein. Studierende in Studiengängen, für die die Hausübung eine Prüfungsvorleistung ist, müssen mindesten 50% der Punkte in den Hausübungen erreichen.