EDS - SS17

(G. Kemnitz, C. Giesemann)

Die Vorlesung führt in den rechnergestützten Entwurf digitaler Schaltungen ein. Behandelt werden das logische und das Zeitverhalten, Automaten und andere Verhaltensmodelle für sequentielle Schaltungen, Rechenwerke, Simulation, Synthese und Logikoptimierung. Im begleitenden Praktikum digitaler Schaltungsentwurf I werden digitale Schaltungen entworfen, simuliert, in programmierbare Logikschaltkreise programmiert und ausprobiert.

Inhalt der Lehrveranstaltung

- Zwei einführende Beispiele: einen Entwurf mit Standardschaltkreisen und einen VHDL-Entwurf für FPGAs.

- Simulation: VHDL, ereignisgesteuerte Simulation, Laufzeittoleranz, ...

- Synthese und Schaltungsoptimierung: synthesegerechte Beschreibung, asyncrone Eingabe, KV-Diagramm, ROBDD.

- Rechenwerke und Operationsabläufe:Addierer, ..., Automaten, serielle Schnittstelle, ...

- Vom Transistor zur Schaltung: MOS-Transistoren, Gatter, Layout, Verzögerung, ...

- Rechner: CORIDC, Minimalprozessor, Pipeline.

Zielgruppe: Bachelor Informatik, Bachelor Technische Informatik

Credits: (ECTS): 6

Foliensätze, Handouts für den Ausdruck und Beispielprogramme

Foliensätze [F], Handouts für den Ausdruck [H] und Beispielprogramme [P]

- [F1] [H1] Einführung

- Standardschaltkreise: Entwurf eines Zählers, Test der Zählfunktion, Zustandsregister, Leiterplattenentwurf.

- VHDL + FPGA: Einfache Gatterschaltung, Zähler und Ampelsteuerung, Simulation.

- [F2] [H2] [P2] Simulation

- Einführung in VHDL: Hallo Welt, Signale, Datentypen, imperative Modelle, ereignisgesteuerte Simulation.

- Strukturbeschreibung: Schnittstellen, Instanziierung und Verbinden von Teilschaltungen, Testrahmen.

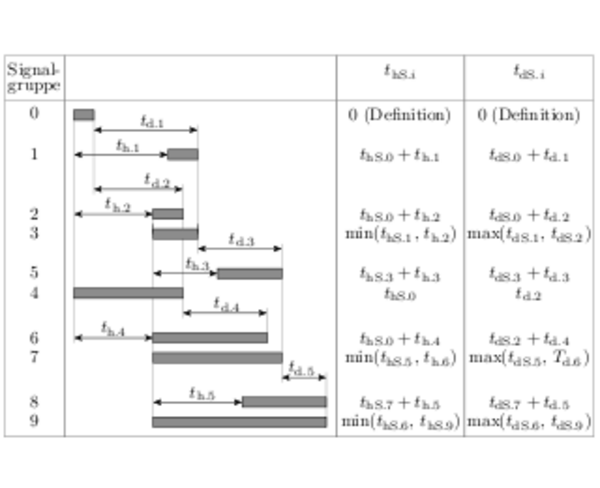

- Laufzeittoleranz: Glitches, Simulation von Zeittoleranzen, Laufzeitanalyse.

- Speicher: Latches, Register, Verarbeitung + Abtastung, Register-Transfer-Funktionen, adressierbare Speicher.

- [F3] [H3] Synthese und Schaltungsoptimierung

- Synthese: Verarbeitungsfunktionen, Register-Transfer-Funktionen, typische Beschreibungsfehler, Constraints.

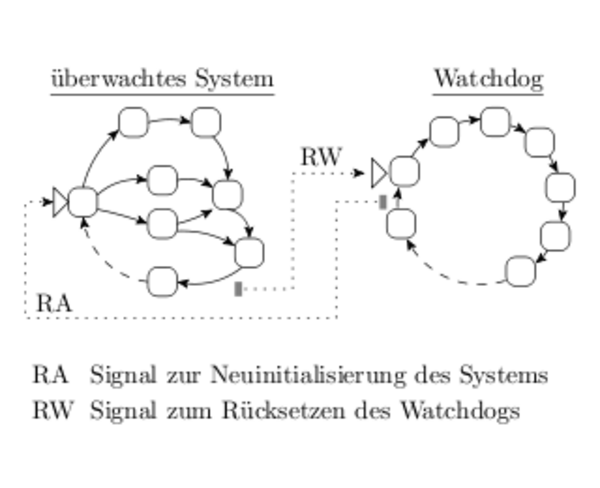

- Asyncrone Eingabe: Abtastung, Initialisierung, Entprellen, asynchrone Schnittstellen mit und ohne Übertragung des Sendertaktes.

- Schaltungsoptimierung: Energieverbrauch, Schaltungsumformung, KV-Diagramm, Verfahren von Quine und McCluskey, reduziertes geordnetes binäres Entscheidungsdiagramm (ROBDD).

- [F4] [H4] [P4] Rechenwerke und Operationsabläufe

- Rechenwerke: Addierer, Subtrahierer, Zähler etc. Multiplizierer, Komparatoren, Block-Shifter.

- Automaten: Entwurf mit KV-Diagrammen, Beschreibung in VHDL, redundante Zustände, Spezifikation und Entwurf.

- Operationsabläufe: serielle Schnittstelle, serieller Addierer, Dividierer.

- [F5] [H5] Vom Transistor zur Logikschaltung

- Gatterentwurf: MOS-Transistoren als Schalter, FCMOS-Gatter, deaktivierbare Treiber, Transfergatter und Multiplexer, geometrischer Entwurf.

- Signalverzögerung: Inverter, Logikgatter, Puffer.

- Latches und Register.

- Blockspeicher: SRAM, Mehrport- und Assoziativspeicher, DRAM, Festwertspeicher.

- Programmierbare Logikschaltkreise.

- [F6] [H6] [P6] Rechnerstrukturen

- CORDIC: Algorithmus, Simulation des Algrithmus, Umstellung auf Festkommazahlen, Entwurf als Rechenwerk, Testrahmen.

- MiPro (Minimalprozessor): Funktion und Befehlssatz, Assembler und Disassembler, Prozessorzustand, Simulationsmodell, Testrahmen, Testbeispiele.

- RISC-Prozessor: Pipeline-Verarbeitung, Simulationsmodell, Testbeispiele.

Literatur

- G. Kemnitz: Technische Informatik Band 2: Entwurf digitaler Schaltungen. Springer. 2011.

- P. J. Ashenden: Designer's Guide to VHDL. Morgan Kaufmann Publishers. 2008.

- J. Reichert, B. Schwarz: VHDL-Synthese: Entwurf digitaler Schaltungen und Systeme. Oldenbourg. 2009

- VHDL-Books