# Rechnerarchitektur, Foliensatz 2 Zeitabläufe

G. Kemnitz

Institut für Informatik, Technische Universität Clausthal 22. Januar 2015

#### Inhalt des Foliensatzes

|     | Pipeline-Verarbeitung     | 2.4 | Aufgaben             |

|-----|---------------------------|-----|----------------------|

| 1.1 | Befehlsabarbeitung        |     | Kontrollfluss        |

| 1.2 | Pipeline-Auslastung       | 3.1 | Sprungbefehle        |

| 1.3 | Lade/Speicher- Pipeline   | 3.2 | Fallunterscheidungen |

| 1.4 | Sprung- Pipeline          | 3.3 | Schleifen            |

| 1.5 | Der Beispielprozessor     | 3.4 | Aufgaben             |

| 1.6 | Aufgaben                  |     | Unterprogramme       |

|     | Speicher                  | 4.1 | Lokale Variablen     |

| 2.1 | ${ m Adressr\ddot{a}ume}$ | 4.2 | Parameterübergabe    |

| 2.2 | Lade- und Speicherbefehle | 4.3 | Rekursion            |

2.3 Konstanteninitialisierung 4.4 Aufgaben

# Pipeline-Verarbeitung

## 1. Pipeline-Verarbeitung

## Pipeline-Verarbeitung (dt. Fließband-Verarbeitung)

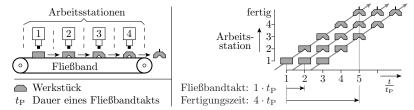

Pipeline-Verarbeitung ist die effektivste Form der Parallelverarbeitung, auch für Rechner:

- Aufteilung der Arbeit in Schritte, die an einem Fließband (engl. Pipeline) abgearbeitet werden.

- Die Bearbeitungszeit je Werkstück ist N Schritte und es wird gleichzeitig an N Werkstücken gearbeitet.

- In jedem Schritt beginnt die Arbeit an einem Werkstück und ein Werkstück wird fertig.

#### Befehlsabarbeitung

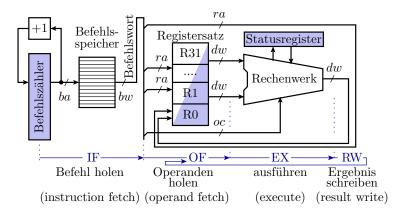

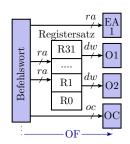

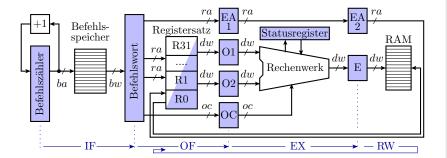

#### Kern eines RISC-Prozessors ohne Pipeline

- Quellregister: Befehlszähler, Status- und Operandenregister.

- Zieleregister: Befehlszähler, Status- und Ergebnisregister.

- Verarbeitungsschritte: Befehl holen, Operanden holen, ...

- G. Kemnitz · Institut für Informatik, Technische Universität Clausthal

### Aufteilung in Pipeline-Phasen

# 1. Pipeline-Verarbeitung

#### 1. Befehlsabarbeitung

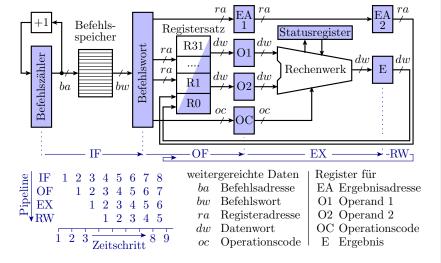

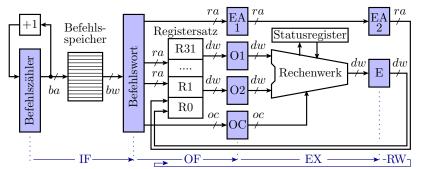

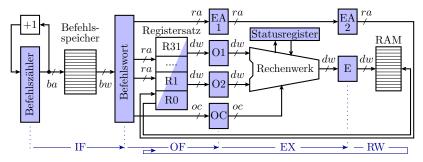

Die Aufteilung der Verarbeitungsschritte in Pipeline-Phasen erfolgt durch Einbau getakteter Register für die Zwischenergebnisse. Pipeline-Phasen im Beispielmodell:

- IF (Instruction Fetch) Befehl holen. Adressierung des Befehlsspeichers vom Befehlszähler und Übernahme des Befehlswortes in das Befehlswortregister.

- OF (Operand Fetch) Operanden holen: Adressierung des Registersatzes mit den Operandenadressen und Übernahme der Registerinhalte in die Operandenregister. Weitergabe der Ergebnisadresse und des Operationscodes an die nächste Pipeline-Phase.

## 1. Pipeline-Verarbeitung

#### 1. Befehlsabarbeitung

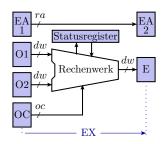

EX (Execute): Befehle Ausführen:

Aus den Operanden und dem

Operationscode bildet das

Rechenwerk das Ergebnis und

speichert es. Weitergabe der

Ergebnisadresse an die nächste

Pipeline-Phase.

RW (Result Write) Ergebnis schreiben: Adressierung des Registersatzes mit der Ergebnisadresse und Speichern des Ergebnisses.

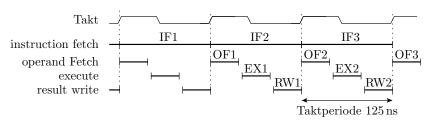

Die Befehlsausführung dauert vier Schritte (Taktperioden). Es wird gleichzeitig an vier Befehlen gearbeitet. Der maximal erzielbare Verarbeitungsdurchsatz ist ein Befehl pro Schritt.

- Bei einer Aufteilung des Verarbeitungsflusses in mehrere gleichlange Pipeline-Phasen kann der Rechner wesentlich schneller getaktet werden und trotzdem in jedem Takt eine neue Operation beginnen und eine fertigstellen.

- Die Fertigstellung der einzelnen Befehle dauert mindest genauso lange wie ohne Pipeline.

#### Pipeline-Auslastung

#### Pipeline-Auslastung

Im Modell kann ein Nachfolgebefehl nur Ergebnisse von mind. 2 Takten zuvor gestarteten Befehlen weiterverarbeiten. Beispiel:

| Addition von vier<br>Registerinhalten                                                           |

|-------------------------------------------------------------------------------------------------|

| 1: $r_0 \leftarrow r_0 + r_1$<br>2: $r_0 \leftarrow r_0 + r_2$<br>3: $r_0 \leftarrow r_0 + r_3$ |

| * Register lesen $n$ lesen und mit $n$ überschreiben                                            |

| IF | ہ<br><b>→</b> – |       | 0     | F     | Ī     | RW | ΕΣ | ζ ] |

|----|-----------------|-------|-------|-------|-------|----|----|-----|

| PC | BR              | $r_0$ | $r_1$ | $r_2$ | $r_3$ | O1 | O2 | Е   |

| 1  |                 | 7     | 2     | 11    | 17    |    |    |     |

| 2  | B1              |       |       |       |       |    |    |     |

| 3  | B2              | *     | *     |       |       | 7  | 2  |     |

|    | В3              | *     |       | *     |       | 7  | 11 | 9   |

|    |                 | *9    |       |       | *     | 7  | 17 | 18  |

|    |                 | 18    |       |       |       |    |    | 24  |

|    |                 | 24    |       |       |       |    |    |     |

In  $r_0$  steht in Takt 5  $r_0 + r_1$ , in Takt 6  $r_0 + r_2$  und in Takt 7  $r_0 + r_3$ . Zur Berechnung von  $r_0 + r_1 + r_2 + r_3$  muss die OF-Phase des Nachfolgebefehl auf den Abschluss der RW-Phase warten.

## Einfügen von nop<sup>1</sup>-Befehlen

Addition von vier Registerinhalten

1:

$$r_0 \leftarrow r_0 + r_1$$

$$4: r_0 \leftarrow r_0 + r_2$$

6: nop 7:

$$r_0 \leftarrow r_0 + r_3$$

| *     | Register lesen |

|-------|----------------|

| $*_n$ | lesen und mit  |

<sup>&</sup>quot;n lesen und mit n überschreiben

|   | _]              | F _ |       | О     | F     | <b>▼</b> ] | RW | ΕΣ | ξ_ |

|---|-----------------|-----|-------|-------|-------|------------|----|----|----|

| [ | $\overline{PC}$ | BR  | $r_0$ | $r_1$ | $r_2$ | $r_3$      | 01 | O2 | Ε  |

|   | 1               |     | 7     | 2     | 11    | 17         |    |    |    |

|   | 2               | B1  |       |       |       |            |    |    |    |

|   | 3               | nop |       |       |       |            |    |    |    |

|   | 4               | nop |       |       |       |            |    |    |    |

|   | 5               | B4  |       |       |       |            |    |    |    |

|   | 6               | nop |       |       |       |            |    |    |    |

|   | 7               | nop |       |       |       |            |    |    |    |

|   |                 | В7  |       |       |       |            |    |    |    |

|   |                 |     |       |       |       |            |    |    |    |

|   |                 |     |       |       |       |            |    |    |    |

|   |                 |     |       |       |       |            |    |    |    |

|   |                 |     |       |       |       |            |    |    |    |

■ Wie lange dauert jetzt die Ausführung der drei Befehle?

<sup>&</sup>lt;sup>1</sup>nop – No OPeration, für den Beispielprozessor Op-Code 0x0000.

## Programmoptimierung

| 1: | $r_0$ | $\leftarrow$ | $r_0$ | + | $r_1$ |

|----|-------|--------------|-------|---|-------|

|    |       |              |       |   |       |

2:  $r_2 \leftarrow r_2 + r_3$

3: nop

4: nop

$5: r_0 \leftarrow r_0 + r_2$

\* Register lesen

n lesen und mit n überschreiben

|    |          |       |       |       | 4     |    |                           |    |

|----|----------|-------|-------|-------|-------|----|---------------------------|----|

| _I | <u> </u> |       | О     | F     |       | RW | $\mathbf{E}^{\mathbf{y}}$ | ζ_ |

| PC | BR       | $r_0$ | $r_1$ | $r_2$ | $r_3$ | 01 | O2                        | Ε  |

| 1  |          | 7     | 2     | 11    | 17    |    |                           |    |

| 2  | В1       |       |       |       |       |    |                           |    |

| 3  | B2       | *     | *     |       |       | 7  | 2                         |    |

| 4  | nop      |       |       | *     | *     | 11 | 17                        | 9  |

| 5  | nop      | 9     |       |       |       |    |                           | 28 |

|    | B5       |       |       | 28    |       | _  |                           |    |

|    |          | *     |       | *     |       | 9  | 28                        |    |

|    |          | 37    |       |       |       |    |                           | 37 |

|    |          | 01    |       |       |       |    |                           |    |

Die Additionen  $r_0 + r_1$  und  $r_2 + r_3$  können direkt nacheinander erfolgen. Berechnung braucht zwei Takte weniger.

#### Fakt 1

Ein Prozessor ist nur so gut wie sein Compiler.

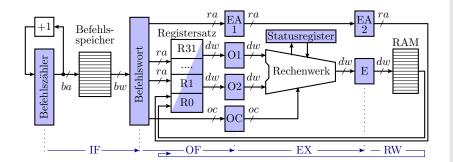

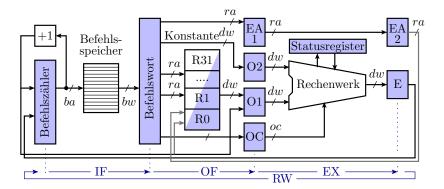

Lade/Speicher- Pipeline

#### 1. Pipeline-Verarbeitung 3. Lade/Speicher- Pipeline

# Ladeoperation

- Erweiterung der RW-Phase um den Datenlesezugriff.

- Die aus dem Speicher gelesenen Daten sind bei dieser Pipeline-Struktur erst drei Befehle später nutzbar<sup>2</sup>.

- Nicht optimierte Befehlsfolge für »Variable +1« ist »Lesen«,  $2\times nop$ «, Addieren,  $2\times nop$ « und Schreiben« (10 Befehle).

<sup>&</sup>lt;sup>2</sup>Es gibt HW-Lösungen, die dieses Pipeline-Problem umgehen. G. Kemnitz · Institut für Informatik, Technische Universität Clausthal

Befehlsfolge für einen einfachen Increment:

. . .

1:

$$r_0 \leftarrow \text{mem}(r_{28} + 4)$$

2: nop

3: nop

4:

$$r_0 \leftarrow r_0 + 1$$

5: nop

6: nop

7:

$$mem(r_{28} + 4) \leftarrow r_0$$

| *  | Register lesen                  |

|----|---------------------------------|

| *n | lesen und mit $n$ überschreiben |

| PC | Befehlszähler                   |

| BR | Befehlsregister                 |

| PC | BR  | $r_0$ | $r_1$ | $r_{28}$ | $r_{29}$ | O1 | O2 | Е |

|----|-----|-------|-------|----------|----------|----|----|---|

| 1  |     | 7     | 2     | 11       | 17       |    |    |   |

| 2  | B1  |       |       |          |          |    |    |   |

| 3  | nop |       |       |          |          |    |    |   |

| 4  | nop |       |       |          |          |    |    |   |

| 5  | B4  |       |       |          |          |    |    |   |

| 6  | nop |       |       |          |          |    |    |   |

| 7  | nop |       |       |          |          |    |    |   |

|    | B7  |       |       |          |          |    |    |   |

|    |     |       |       |          |          |    |    |   |

|    |     |       |       |          |          |    |    |   |

|    |     |       |       |          |          |    |    |   |

|    |     |       |       |          |          |    |    |   |

| IF | ק   |       | O     | F        | 1        | RW | ΕΣ | ζ |

#### Speicheroperation

Im Unterschied zur Ladepoperation ist in der Ex-Phase die Übertragungsrichtung vom Registersatz zum RAM.

## 1. Pipeline-Verarbeitung 3. Lade/Speicher- Pipeline

■ Wie viele nop-Befehle müssen zwischen einem Speicherbefehl  $mem(r_{28}+4)\leftarrow r_0$  und einem Lesebefehl

$$r_4 \leftarrow \operatorname{mem}(r_{28} + 4)$$

für dieselbe RAM-Adresse eingefügt werden, damit der geschriebene Wert gelesen wird?

#### Sprung- Pipeline

#### Sprung-Pipeline

Bei Ausführung eines Sprungs wird der Befehlszähler in der IF-, der OF- und der EX-Phase incrementiert. Erst nach der RW-Phase steht das Sprungziel im Befehlszähler<sup>3</sup>.

<sup>3</sup>Die Zeitscheiben nach einem Sprungbefehl, die noch linear abgearbeitet werden, heißen » Delay-Slots«.

#### 4. Sprung- Pipeline

Abarbeitung eines Sprungs in der Pipeline:

|                                               |      | PC   | $_{\rm BR}$ | $r_0$ | $r_1$ | $r_{28}$ | $r_{29}$ | O1 | O2                  | Е                               |

|-----------------------------------------------|------|------|-------------|-------|-------|----------|----------|----|---------------------|---------------------------------|

| $0x20: PC \leftarrow PC + 0x10$               | (B1) | 0x20 |             | 7     | 2     | 11       | 17       |    |                     |                                 |

| $0x21: r_0 \leftarrow r_0 + 3$                | (B2) | 0x21 | В1          |       |       |          |          |    |                     |                                 |

| $0x22: r_1 \leftarrow r_1 \wedge 3$           | (B3) | 0x22 | B2          |       |       |          |          |    |                     |                                 |

| $0x23: r_0 \leftarrow \text{mem}(r_{28} + 4)$ | (B4) | 0x23 | В3          |       |       |          |          |    |                     |                                 |

| •••                                           |      | 0x30 | B4          |       |       |          |          |    |                     |                                 |

| $0x30: r_0 \leftarrow r_0 + r_1$              | (B5) |      |             |       |       | *        |          |    |                     |                                 |

|                                               |      |      |             |       |       |          |          | 11 | 4                   |                                 |

|                                               |      |      |             |       |       |          |          |    |                     | 15                              |

| * Register lesen                              | 1    |      |             | 34    |       |          |          |    |                     |                                 |

| rtegister lesen                               |      |      |             |       |       |          |          |    |                     |                                 |

| $*_n$ lesen und mit $n$ überschreiben         |      |      |             |       |       |          |          |    |                     |                                 |

|                                               |      |      |             |       |       |          |          |    |                     |                                 |

| PC Befehlszähler                              |      |      |             |       |       |          | _        |    |                     |                                 |

| BR Befehlsregister                            |      | IF   | ` <u> </u>  |       | О     | F        |          | RW | $\mathbf{E} \Sigma$ | $\begin{bmatrix} \end{bmatrix}$ |

Der typische RISC-Prozessor hat nur null bis max. zwei Delay-Slots. Das wird durch überspringen von Pipeline-Phasen (Ergebnis-Forwarding) oder durch Anhalten der Pipeline erreicht. Der Beispielprozessor

5. Der Beispielprozessor

#### Unser Beispielprozessor ATmega 2560

Befehl holen (IF) dauert einen Takt. Operanden holen (OF),

Ausführen (EX) und Ergebnis schreiben (RW) dauern nur <sup>1</sup>/<sub>3</sub>

Takt.

- Operationsergebnisse für Folgeoperation verfügbar, d.h. lückenlose Abarbeitung ohne nop-Befehle möglich.

- Lade-, Speicher- und Sprungbefehle sowie die Multiplikation benötigen mindestens zwei Takte.

#### Aufgaben

#### Aufgabe 2.1: Addition von fünf Registerwerten

Die Werte der Register r0 bis r4 sollen in der Verarbeitungs-Pipeline auf Folie 7 addiert und die Ergebnisse in Register r2 gespeichert werden. Entwickeln Sie dafür ein möglichst kurzes Programm und füllen Sie in Anlehnung an Folie 14 die nachfolgende Tabelle aus.

|                       | <u>II</u> | 7             | _     | О     | F     |       |       | RW | ΕΣ | Ţ ] |

|-----------------------|-----------|---------------|-------|-------|-------|-------|-------|----|----|-----|

| BefAdr. Operation     | on PC     | BR            | $r_0$ | $r_1$ | $r_2$ | $r_3$ | $r_4$ | 01 | O2 | Е   |

| 1<br>2<br>3<br>4<br>: | 1 2 :     | B1<br>B2<br>: | 38    | 42    | 13    | 29    | 4     |    |    |     |

Ab dem wie vielten Befehl ist die Summe 38 + 42 + 13 + 29 + 4 in Register  $r_0$  verfügbar?

# Speicher

#### Speicher

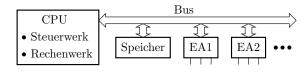

Ein Universalrechner besteht aus

- Prozessor (CPU Central Processing Unit)

- Speicher(n) und

- EA- (Ein-/Ausgabe-, IO- (Input-/Output-) Registern.

Im Speicher hat jeder Befehl und jedes Datenobjekt eine Adresse. Die EA-Register sind wie ein Speicher organisiert. Befehle, Daten und EA-Register können sich einen Adressraum teilen, getrennte Adressräume besitzen oder in mehrere Adressräume auf unterschiedlichen Adressen eingeblendet sein. Bei mehreren Adressräumen erfolgt die Adressraumauswahl (Registeradresse, EA-Adresse, Befehlsadresse, ...) über den Befehl.

#### Adressräume

#### Adressaufteilung

Die Größe der Adressräume richten sich nach der Breite der Register und der Größe der Adresskonstanten in den Befehlsworten.

- 8-Bit Mikrorechner haben typ 16-Bit-Adressregister und 64-kByte Adressräume, u.U. auch mehrere über Zusatzregister oder die Befehlsart auswählbare.

- 32-Bit Prozessoren haben typ. einen gemeinsamen 4 GByte Adressraum für Befehle, Daten und EA-Register.

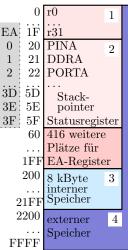

#### Beispielprozessor Atmega 2560:

- 17-Bit-Befehlszähler, 128 k×2 Byte großer Befehlsspeicher.

- 6-Bit IO-Adressen, 64 über IN-/OUT-Befehle ansprechbare EA-Register.

- 16-Bit Adressregister, 16-Bit-Datenadresskonstanten, 64 kByte Datenadressraum, in dem die Arbeits- und EA-Register mit eingeblendet sind.

## Daten- und EA-Adressen des ATmega 2560

- Arbeitsregister für Verarbeitungsbefehle.

- 2 Mit in Rd, k; k 6-Bit Adresse out k, Rd;

les- und schreibbare EA-Register (IO-Adresse k gleich RAM-Adresse minus 0x20).

3 Der Compiler vergibt die Adressen 0x200 aufsteigend für globale Variablen und nutzt die Adressen von 0x21FF absteigend als Stack.

von 0x21FF absteigend als Stack.

1 Mit einer speziellen EA-Bit-Einstellung ist auch der Bereich von 0-0x21FF des externen Speichers les- und beschreibbar.

Lade- und Speicherbefehle

#### Adressierungsarten

Schnellzugriff auf kleine Teiladressbereiche:

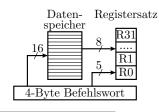

- Registeradressen (5 Bit): Bis zu zwei Registeradressen je Verarbeitungsbefehl, eine je Lade-/Speicherbefehl, ...

- IO-Adressen (6 Bit): Zugriff auf eines von 64 EA-Registern.

Der Zugriff auf den kompletten 16-Bit Adressraum erfolgt mit Lade- und Speicherbefehlen mit unterschiedlichen

#### Adressierungsarten:

- direkt: Adressierung mit einer 16-Bit Konstante aus dem Befehlswort (erfordert 4-Byte Befehlsworte).

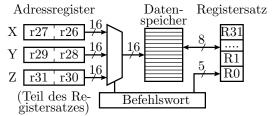

- indirekt: Adressierung mit 16-Bit Register  $(X, Y \text{ oder } Z)^4$ .

- Indirekt mit Verschiebung: Adressierung mit einem 16-Bit-Register plus Konstante aus dem Befehlswort.

<sup>&</sup>lt;sup>4</sup>Das sind Registerpaare: X=(r27:r26), Y=(r29:r28) und Z=(r31,r30).

#### Direkte Adressierung

Codierung der 16-Bit Speicheradresse im Befehlswort. Verlangt Doppelbefehlsworte.

| Operation | TZ | OpCode              | Assembler |

|-----------|----|---------------------|-----------|

| Rd←(k)    | 2  | 1001 000d dddd 0000 | lds Rd, k |

|           |    | kkkk kkkk kkkk kkkk |           |

| (k)←Rd    | 2  | 1001 001d dddd 0000 | sts k, Rd |

|           |    | kkkk kkkk kkkk kkkk |           |

(TZ - Verarbeitungstaktzyklen; (k) - Datenspeicherinhalt Adresse k).

#### Beispiel:

ldi r1, 21 ; r1 $\leftarrow$ 21 lds r2, 0x200; r2 $\leftarrow$ (0x200) add r2, r1 ; r2 $\leftarrow$ r2 + r1 sts r2, 0x200

#### Indirekte Adressierung

Adressierung mit einem der 16-Bit-Adressregister, die je aus einem Paar der oberen Arbeitsregister gebildet werden.

| Operation         | TZ | OpCode              | Assembler |

|-------------------|----|---------------------|-----------|

| $Rd\leftarrow(X)$ | 2  | 1001 000d dddd 1100 | ld Rd, X  |

| Rd←(Y)            | 2  | 1000 000d dddd 1000 | ld Rd, Y  |

| Rd←(Z)            | 2  | 1000 000d dddd 0000 | ld Rd, Z  |

| (X)←Rr            | 2  | 1001 001r rrrr 1100 | st X, Rr  |

|                   |    |                     |           |

# 2. Speicher

Die indirekte Adressierung gibt es auch mit

- Post-Increment:  $Rd \leftarrow (X)$ ;  $X \leftarrow X+1$ ;

- Pre-Decrement:  $X \leftarrow X-1$ ;  $Rd \leftarrow (X)$ ;

(auch für Y und Z) sowie mit Verschiebung

$$Rd\leftarrow(Y+q)$$

(nur für Y und Z). Assemblernotationen:

ld Rd, X+; Rd

$$\leftarrow$$

(X); X  $\leftarrow$ X+1

ld Rd, -X; X  $\leftarrow$ X-1; Rd  $\leftarrow$ (X)

1dd Rd, Y+q; Rd

$$\leftarrow$$

(Y+q)

st X+, Rr;

$$(X)\leftarrow Rr$$

;  $X\leftarrow X+1$

st -X, Rr;

$$X \leftarrow X-1$$

;  $(X) \leftarrow Rr$

std Y+q, Rr;

$$(Y+q)\leftarrow Rr$$

Anwendungsbeispiel: Kopieren einer Zeichenkette:

|                  | :  |    |    | Ze | ich | enke | ette | a  |    |    |    | : Z  | eicl | ı. b |  |

|------------------|----|----|----|----|-----|------|------|----|----|----|----|------|------|------|--|

| Adresse - 0x200  | 0  | 1  | 3  | 4  | 5   | 6    | 7    | 8  | 9  | Α  | В  | С    | D    |      |  |

| Ascii-Zeichen    | Н  | a  | 1  | 1  | 0   |      | W    | е  | 1  | t  | \0 | frei |      |      |  |

| Wert hexadezimal | 48 | 61 | 6C | 6C | 6F  | 20   | 57   | 56 | 6C | 74 | 00 |      |      |      |  |

|                  | Zeichenkette a |    |    |    |    |    |    | Zeich. b |    |    |    |      |   |  |             |

|------------------|----------------|----|----|----|----|----|----|----------|----|----|----|------|---|--|-------------|

| Adresse - 0x200  | 0              | 1  | 3  | 4  | 5  | 6  | 7  | 8        | 9  | Α  | В  | С    | D |  |             |

| Ascii-Zeichen    | Н              | a  | 1  | 1  | 0  |    | W  | е        | 1  | t  | \0 | frei |   |  | b<br>-<br>- |

| Wert hexadezimal | 48             | 61 | 6C | 6C | 6F | 20 | 57 | 56       | 6C | 74 | 00 |      |   |  |             |

Das Kopieren einer Zeichenkette lässt sich in C sehr kompakt mit zwei Zeigerregistern mit Post-Inkrement LS-Operationen beschreiben.

```

#include <avr/io.h>

Name

Value

10

{uint8_t[11]{data}@0x0200}

[0]

0x48

11

uint8 t a[] = "Hallo Welt";

[1]

0x61

12

uint8 t b[10];

[2]

0x6c

13

□int main(void){

[3]

0x6c

14

uint8 t *p1=a;

[4]

0x6f

15

uint8 t *p2=b;

[5]

0x20

16

while (*p1){

17

*(p2++) = *(p1++);

[9]

0x74

18

[10] 0x00

19

{uint8_t[10]{data}@0x020c}

```

#### Übersetzung mit Compileroptimierung -O1

```

while (*p1)

16

17

*(p2++) = *(p1++);

00092

LDS R24,0x0200 r_{24} \leftarrow a[0]

00094

Flags C, Z, ... entsprechend r_{24} setzen

TST R24

BREO PC+0 \times 09 wenn a[0]==0, überspringe Schleife

00095

00096

LDI R26,0x01 | lade X mit 0x201

LDI R27.0\times02 (Adresse von a[1])

00097

LDI R30,0x0C | lade Z mit 0x20C

00098

LDI R31,0x02

(Adresse von b[0])

00099

0009A

\mathsf{ST} \ \mathsf{Z+}_{\mathsf{R}} \mathsf{R24} \qquad (Z) \leftarrow r_{24}; \ Z \leftarrow Z+1

LD R24,X+ r_{24} \leftarrow (X); X \leftarrow X+1

0009B

CPSE R24,R1 überspringe Folgebefehl, wenn r_{24} == r_1 \ (r_1 \ \text{is} \ 0) RJMP PC-0x0003 springe nach 0x9A

0009C

```

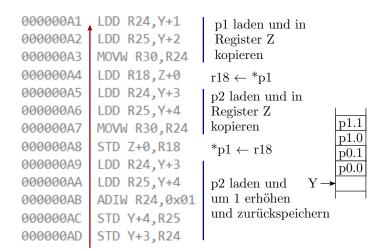

#### Übersetzung mit Compileroptimierung -O0

Y: Framepointer für lokale Variablen (siehe später ab Folie 77).

# Speicher

```

000000AE

LDD R24,Y+1

LDD R25,Y+2

000000AF

p1 laden und

um 1 erhöhen

ADIW R24,0x01

000000B0

und zurückspeichern

000000B1

STD Y+2,R25

000000B2

STD Y+1,R24

000000B3

LDD R24,Y+1

p1 laden und in

000000B4

LDD R25,Y+2

Register Z

kopieren

000000B5

MOVW R30, R24

r24 \leftarrow *p1

000000B6

LDD R24,Z+0

000000B7

TST R24

Wert testen, wenn nicht 0,

000000B8

BRNF PC-0x17

Sprung zum Schleifenbeginn

```

#### Mit -O0 übersetzte Programme:

- gliedern sich in Hochsprachenberechnungsschritte.

- In jedem Schritt werden die Daten aus dem Speicher geholt und die Ergebnisse in den Speicher geschrieben.

- Erlaubt Schrittbetriebest des C-Programms.

## 2. Speicher

```

Value

#include <avr/io.h>

Name

{uint8_t[11]{data}@0x0200}

10

[0]

0x48

11

uint8_t a[] = "Hallo Welt";

[1]

0x61

12

uint8 t b[10];

[2]

0x6c

13

□int main(void){

[3]

0x6c

14

uint8 t *p1=a;

[4]

0x6f

uint8 t *p2=b;

15

[5]

0x20

16

while (*p1){

17

*(p2++) = *(p1++);

[9]

0x74

18

[10] 0x00

19

{uint8_t[10]{data}@0x020c}

```

Das mit -O1 übersetzte Programm verwendet für die innere Schleife die minimale Befehlsfolge:

```

; loop ist eine Marke der Programmadresse

loop:

st Z+, r24

ld r24, X+

cpse r24, r1; Compare Skip Even

rjmp loop ; springe zurück zur Marke »loop«

```

Es gibt weitere Arten der Optimierung, z.B. die Vorgabe, für die Zeiger Register zu benutzen. Der Compiler nimmt dann aber

nicht unbedingt die Register X, Y und Z, so dass das Programm nicht deutlich besser wird.

Selbst Probieren!

#### Konstanteninitialisierung

#### Speichern von Konstanten

Konstanten, die auch nach Neueinschalten des Prozessors noch vorhanden sein sollen, z.B. der Text »Hallo Welt« im Beispiel zuvor, müssen im Programmspeicher abgelegt und beim Programmstart in den Datenspeicher kopiert werden.

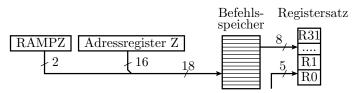

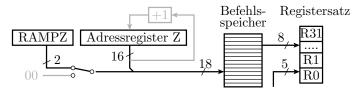

Die Adressierung des 256kByte-Befehlsspeichers erfolgt indirekt mit einer 18-Bit Adresse. Die niederwertigen 16 Adressbits werden aus Register Z und die oberste 2 Bit aus EA-Register RAMPZ (EA-Adresse 0x3B) genommen.

#### Befehlsvariationen:

- höchste Adressbits 00 statt der Bits RAMPZ(1:0)

- mit Post-Inkrement

| Operation                              | TZ | OpCode              | Assembler   |

|----------------------------------------|----|---------------------|-------------|

| Rd←p(Z)                                | 3  | 1001 000d dddd 0100 | lpm Rd, Z   |

| $Rd \leftarrow p(Z); Z \leftarrow Z+1$ | 3  | 1001 000d dddd 0101 | lpm Rd, Z+  |

| Rd←p(RAMPZ:Z)                          | 3  | 1001 000d dddd 0110 | elpm Rd, Z  |

| Rd←p(RAMPZ:Z);                         | 3  | 1001 000d dddd 0111 | elpm Rd, Z+ |

| Z←Z+1                                  |    |                     |             |

(p(..) – Programmspeicherinhalt von ..)

## 2. Speicher

```

Beim übersetzen des

11

uint8 t a[] = "Hallo Welt";

Programms rechts schreibt

12

uint8 t b[10];

der Compiler die Zeichen-

13

□int main(void){

kettenkonstante »Hallo

14

uint8 t *p1=a;

15

uint8 t *p2=b;

Welt« hinter die Endlos-

while (*p1){

16

schleife des Startup-

*(p2++) = *(p1++);

17

Codes ab Adresse 0xA1:

```

```

Zeichenkettenkonstante dissassembliert als Ascii-Text

0000000A1 48.61

ORI R20,0x18

Ha

000000A2 6c.6c

ORI R22,0xCC

11

000000A3 6f.20

AND R6,R15

Оп

000000A4 57.65

ORI R21,0x57

We

000000A5 6c.74

ANDI R22,0x4C

lt

0/

000000A6 00.00

NOP

```

Der Disassembler kann Zeichenketten nicht von Programmcode unterscheiden.

Die Adressierung als Datenbytes erfolgt mit 18 Bit. Die beiden höchstwertigen Bits stehen im EA-Register RAMPZ (Adr. 0x5B). Initialisierungsschleife für das Feld a:

```

00007A

LDI R17,0x02

r17 \leftarrow 2

00007B

LDI R26,0x00

LDI R27,0x02

00007C

00007D LDI R30,0x42

Z \leftarrow 0x142

00007E LDI R31,0x01

00007F

LDI R16,0x00

RAMPZ \leftarrow 0

000080

OUT 0x3B,R16

000081

RJMP PC+0x0003

000082

A ELPM R0,Z+

r0 \leftarrow PMem(Z); Z \leftarrow Z+1

000083

ST X+,R0

DMem(X) \leftarrow r0; X \leftarrow X+1

000084

CPI R26,0x0C

Teste, ob X \neq 0x20C ist. Wenn

CPC R27, R17

000085

ja, Spring zu Adresse 0x82

BRNE PC-0x04

000086

```

vereinbarte Feld, das der Compiler ab Adresse 0x20C platziert hat, wird mit Nullen initialisiert:

### Aufgaben

#### Aufgabe 2.2: Load-/Store-Befehle

|                         |       |                | a           | D | С | a |

|-------------------------|-------|----------------|-------------|---|---|---|

| Das nachfolgende Pro-   | 0008A | LDI R24,0x63   |             |   |   |   |

| gramm arbeitet mit vier | 0008B | LDI R25,0x01   |             |   |   |   |

| Variablen: a (uint16 t) | 0008C | STS 0x0202,R25 |             |   |   |   |

| Adresse 0x202:0x201,    | 0008E | STS 0x0201,R24 |             |   |   |   |

| ,                       | 00090 | LDI R24,0xF1   |             |   |   |   |

| b (uint8_t) Adresse     | 00091 | STS 0x0200,R24 |             |   |   |   |

| $0x200, c (uint16_t)$   | 00093 | LDS R24,0x0200 |             |   |   |   |

| Adresse Y+3:Y+2 und     | 00095 | ORI R24,0x34   |             |   |   |   |

| d (uint8 t) Adresse     | 00096 | STD Y+1,R24    |             |   |   |   |

| Y+1. Bestimmen Sie      | 00097 | LDS R24,0x0200 |             |   |   |   |

|                         | 00099 | MOV R24,R24    |             |   |   |   |

| für jeden Befehl,       | 0009A | LDI R25,0x00   | DI R25,0x00 |   |   |   |

| welche Werte die Vari-  | 0009B | ANDI R24,0xF5  |             |   |   |   |

| ablen nach Ausführung   | 0009C | ANDI R25,0x01  |             |   |   |   |

| haben.                  | 0009D | STD Y+3,R25    |             |   |   |   |

|                         | 0009E | STD Y+2,R24    |             |   |   |   |

#### Aufgabe 2.3: Zeichenketteninitialisierung

Die Befehlsfolge rechts initialisiert eine Zeichenkettenvariable.

- Von welchen Befehlen und mit welchen Werten werden die Zeigerregister X und Z vor

- Wie lautet die Abbruchbedingung der Schleife?

der Schleife initialisiert?

■ Welche Anfangs- und Endadresse hat die Zeichenkettenvariable und mit welchem

Ascii-Text wird sie initialisiert?

Hinweis: Die Umrechnung in Ascii-Zeichen finden Sie mit Google unter dem Stichwort » Ascii-Tabelle«.

0007A LDI R17,0x02 LDI R26,0x00 0007B 0007C LDI R27,0x02

0007D

00082

00083

00084

00085

00086

LDI R30,0x20 0007E LDI R31,0x01 0007F LDI R16,0x00 00080 OUT 0x3B,R16 00081 RJMP PC+0x0003

LPM R0,Z+

ST X+,R0 CPI R26,0x0A CPC R27, R17 BRNF PC-0x04

00091 6c.66 00092 65.74 00093 65.78

00090 48.69

## Kontrollfluss

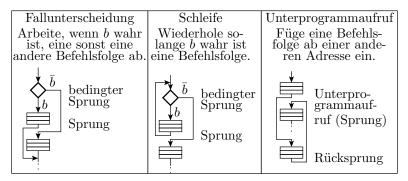

#### Kontrollstrukturen

Der Kontrollfluss in Hochsprachen wird durch Fallunterscheidungen, Schleifen und Unterprogrammaufrufe beschrieben. Diese lassen sich durch unbedingte und bedingte Sprünge im Verarbeitungsfluss nachbilden.

### Sprungbefehle

#### Unbedingte Sprünge

Es gibt drei Arten der Sprungzielvorgabe:

- direkt: Sprungziel ist eine Konstante im Befehlswort.

- indirekt: Sprungziel wird aus Registern gelesen.

- relativ: Sprungdistanz ist eine Konstante im Befehlswort.

| Operation | TZ | OpCode              | $\mathbf{Assembler}$ |

|-----------|----|---------------------|----------------------|

| PC←k      | 3  | 1001 0100 0000 110k | jmp k                |

|           |    | kkkk kkkk kkkk kkkk |                      |

| PC←0:Z    | 2  | 1001 0100 0000 1001 | ijmp                 |

| PC←EIND:Z | 2  | 1001 0100 0001 1001 | eijmp                |

| PC←PC+1+k | 2  | 1100 kkkk kkkk kkkk | rjmp                 |

(PC – Befehlszähler (Program Counter); Z – 16-Bit Adressregister aus r31 und r30; EIND – Verlängerungsregister für Z auf 17 Bit für indirekte Sprünge (EA-Adresse 0x3C); k – 12-Bit-Sprungdistanz, WB:  $-2048 \le k \le 2047$ ).

#### Skip-Befehle

Skip-Befehle überspringen bei erfüllter Bedingung den Nachfolgebefehl, der zwei oder vier Byte lang sein kann.

| Skip-Bedingung     | TZ | OpCode              | ${ m Assembler}$ |

|--------------------|----|---------------------|------------------|

| Rd=Rr              | *  | 100100rd dddd rrrr  | cpse Rd,Rr       |

| Bit b in Rr        | *  | 1111 111r rrrr Obbb | sbrs Rr,b        |

| gesetzt            |    |                     |                  |

| Bit b, Rr gelöscht | *  | 1111110r rrrr 0bbb  | sbrc Rr, b       |

| Bit b, IO-Reg. A   | *  | 1001 1001 AAAA Abbb | sbis A,b         |

| eins               |    |                     |                  |

| Bit b in IO-Reg. A | *  | 10011011 AAAA Abbb  | sbic A,b         |

| null               |    |                     |                  |

<sup>(\* 1</sup> Takt bei nicht erfüllter Bedingung, 2 Takte, wenn ein 2-Byte-, und 3 Takte, wenn ein 4-Byte-Befehl übersprungen wird. A - IO-Register 0 bis 31).

#### Betragsbildung mit Skip-Befehl

```

00008A IN R24,0x00

11

int8_t a;

00008B | SBRC R24,7

□void main(void){

00008C

NEG R24

13

a = PINA;

00008D $\footnote{\text{STS}} 0x0200, R24

14

if (a<0) a=-a;

00008F LDS R24,0x0200

15

PORTC = a;

000091 OUT 0x08,R24

16

000092

RFT

```

- Der in r24 eingelesene Wert ist negativ, wenn das führende Bit (7) eins ist.

- Der Skip-Befehl überspringt die nachfolgende Negation, wenn r24, Bit 7 null ist.

(Das Programm wurde mit Compiler-Optimierung -O2 übersetzt, weil auch bei -O1 noch einen bedingten Sprung verwendet wird.)

#### Bedingte Sprünge

brbs b, k; Sprung, wenn Bit b in SREG eins ist. brbc b, k; Sprung, wenn Bit b in SREG null ist.

Identische Befehle mit bedeutungsorientierten Bezeichnern:

br<Bed> k; Sprung, wenn <Bed> erfüllt ist

| b |   | SREG(b) = 1                               | SREG(b) = 0                                |

|---|---|-------------------------------------------|--------------------------------------------|

| 0 | С | brcs (if Carry Set),                      | brcc (if Carry Clear),                     |

|   |   | brlo (if Lower <sup>(u)</sup> )           | brsh (if Same or Higher <sup>(u)</sup> )   |

| 1 | Z | breq (if Equal)                           | brne (if Not Equal)                        |

| 2 | N | brmi (if Minus <sup>(s)</sup> )           | brpl (if Plus <sup>(s)</sup> )             |

| 3 | V | brvs (if Overflow is Set <sup>(s)</sup> ) | brvc (if Overflow Cleared <sup>(s)</sup> ) |

| 4 | S | brge (Greater or Equal <sup>(s)</sup> )   | brlt (Less Than <sup>(s)</sup> )           |

| 5 | Н | brhs (if Half Carry is Set)               | brhc (if Half Carry Cleared)               |

| 6 | Т | brts (if T flag is Set)                   | brtc (if T flag is Cleared)                |

| 7 | I | brhs (if Interrupt Enabled)               | brhc (if Interrupt Disabled)               |

Die bedingten Sprünge werten ein Bit aus dem Statusregister (EA-Adresse 0x3F) aus und führen bei erfüllter Bedingung relative Sprünge  $PC \leftarrow PC + 1 + k \text{ mit } -64 \le k \le 63 \text{ aus.}$

Beispiel: »Betragsbildung mit -O1«

```

0008A

IN R24,0x00

int8 t a=-9;

0008B

TST R24

12 ⊡void main(void){

0008C .

BRIT PC+0x04

13

a = PINA;

0008D

STS 0x0200, R24

14

if (a<0) a=-a;

0008F

RJMP PC+0x0004

15

PORTC = a;

00090

NEG R24

16

00091

STS 0x0200, R24

■ »tst r24« (TeST for zero or

00093

LDS R24,0x0200

minus) testet den in r24

00095

OUT 0x08,R24

eingelesenen Wert und setzt

00096

RET

die Flags Z, N und S.

```

- »brlt PC+4« springt, bei r24<0 zu Adresse 0x91.

- ... (10 Befehle, statt 7 bei Optimierung mit -O2)

#### Fallunterscheidungen

#### Fallunterscheidung mit if, else if und else

0007D

```

LDI R25,0x2A

Schreiben der 3 Aus-

12 ⊡void main(void){

0007F

LDI R19,0x85

gabewerte in Register

13

register uint8_t a;

0007F

LDI R18,0x1D

14

while (1){

00080 A A IN R24,0x00

a \leftarrow PINA

15

a = PINA;

wenn a < 3?

00081

CPI R24,0x03

16

if (a<3)

BRCC PC+0x03

springe nach else-if

00082

17

PORTC = 0x2A;

OUT 0x08, R25 PORTC \leftarrow 0x2A

00083

18

else if (a<9)

00084

RJMP PC-0x0004

19

PORTC = 0x1D;

CPI R24,0x09 | wenn a < 9?

00085

springe nach else ...

20

else

BRCC PC+0x03

00086

21

PORTA = 0x85:

00087

OUT 0x08, R18 PORTC \leftarrow 0x1D

22

99988

RJMP_PC-0x0008

23

00089

OUT 0x02,R19 PORTA \leftarrow 0x85

0008A

RJMP PC-0x000A

```

(Übersetzt mit -O1).

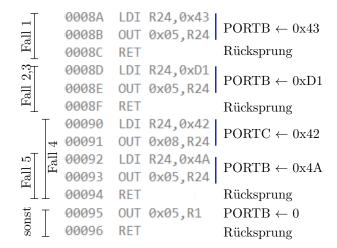

#### Fallunterscheidung mit Case

```

a \leftarrow PINA

11 ⊡void main(void){

0007D

IN R24,0x00

12

uint8 t a = PINA;

0007E

CPI R24,0x04

wenn a>4

13

switch (a){

gehe zu 0x85

0007F

BRCC PC+0x06

14

case 1:

CPI R24,0x02

00080

sonst wenn a>2

15

PORTB = 0x43;

gehe zu 0x8D

00081

BRCC PC+0x0C

16

break;

00082 CPI R24,0x01

wenn a \neq 1

17

case 2:

gehe zu 0x93

00083

BRNF PC+0x12

18

case 3:

gehe zu 0x8A

00084

RJMP PC+0x06

19

PORTB = 0xD1;

00085

CPI R24,0x04

wenn a=4

20

break:

gehe zu 0x90

BREQ PC+0x0A

00086

21

case 4:

00087

CPI R24,0x05

wenn a=5

22

PORTC = 0x42;

gehe zu 0x95

00088

BRNE PC+0x0D

23

case 5:

00089

RJMP PC+0x09

gehe zu 0xA2

24

PORTB = 0x4A:

25

break;

Fall

2.3

4

5

sonst

default:

26

Adresse

0x8A \mid 0x8D \mid

0x92

0x95

0x90

27

PORTB = 0;

PORTB

0x43

0xD1

0x4A

0x4A

0

PORTC

0x42

```

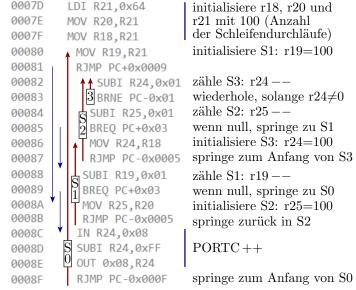

#### Schleifen

#### Warteschleife

Ziel sei ein kleines Programm, das PORTC so langsam hochzählt, dass es mit Leuchtdioden beobachtbar ist.

- Bei 8 Millionen Takten pro Sekunde soll der Prozessor zyklisch ca. 4 Millionen Takte nichts tun und dann den Ausgabewert um eins erhöhen.

- Lösungsansatz: Endlosschleife mit drei verschachtelten Wiederholschleifen

```

wiederhole immer

12 ⊡void main(void){

S0

register uint8_t a, b, c;

wiederhole 100 mal

(S1)

13

while (1){

wiederhole 100 mal

(S2)

14

wiederhole 100 mal (S3)

15

for (a=0; a<100; a++){

tue 4 Schritte nichts*

for (b=0; b<100; b++){}

16

for (c=0; c<100; c++){}

erhöhe PORTC um ein

17

* 4 Schritte insgesamt mit

20

PORTC += 1:

Zähl- und Sprungoperation

```

#### ■ Mit -O1 erzeugtes Maschinenprogramm:

#### Aufgaben

#### Aufgabe 2.4: Sprungbedingung

Welches Statusbit werten die nachfolgenden bedingten Sprünge aus und bei welchem Bitwert wird der Sprung ausgeführt? Bezieht sich der Vergleich auf vorzeichenfreie oder vorzeichenbehaftete Zahlen?

- brlt (Branch if Less Then)

- 2 brpl (Branch if Plus)

- 3 brlo (Branch if Lower)

Das Statusregister des ATmega2560:

Bitnummer: 7 6 5 4 3 2 1 0 Bitname: I T H S V N Z C

C – Carry Flag, Z – Zero Flag, N – Negative Flag, V – Überlauf Zweierkomplement, S – Vorzeichen Zweierkomplement, H – Half Carry, T – Zwischenspeicher Bitkopieren, I – globale Interrupt-Freigabe.

#### Aufgabe 2.5: Reengineering If-Anweisung

Die nachfolgenden Assemblerprogrammausschnitte stammen von einem C-Programm:

```

(u)int8_t a; // Adresse 0x201

(u)int8_t b; // Adresse 0x200

...

if (a ?? b) PORTA = 0x3;

```

Bestimmen Sie aus der verwendeten Sprunganweisung, ob a und b als vorzeichenbehaftet oder vorzeichenfrei vereinbart waren und welche Vergleichsoperation für ?? im C-Programm stand?

```

00085

LDS R25,0x0201

00085

LDS R25,0x0201

00087

LDS R24,0x0200

00087

LDS R24,0x0200

00089

CP R24,R25

00089

CP R24,R25

0008A

BRCC PC+0x03

a)

0008A

BRLT PC+0x03

b)

```

#### Aufgabe 2.6: Reengineering Switch-Anweisung

```

Ergänzen Sie in dem nachfolgenden

0007D

IN R24,0x00

C-Programm die fehlenden Konstanten

0007E

CPI R24,0x15

K1 bis K6 anhand des zugehörigen

0007F

BREQ PC+0x05

Assemblerprogramms, in das der

00080

CPI R24,0x38

Compiler die dargestellte Switch-

00081

BREO PC+0x06

00082

CPI R24,0x12

Anweisung übersetzt hat.

00083

BRNE PC+0x07

00084

LDI R24,0x27

□void main(){

OUT 0x08, R24

00085

switch (PINA) {

12

00086

RFT

13

case K1:

00087

LDI R24,0x44

14

case K2:

PORTC = K4; break;

00088

OUT 0x08, R24

15

case K3:

PORTC = K5; break;

00089

RET

16

default:

PORTC = K6;

0008A

LDI R24,0x22

17

0008B

OUT 0x08, R24

PINA hat Adresse 0

18

PORTC hat Adresse 8

0008C

RET

```

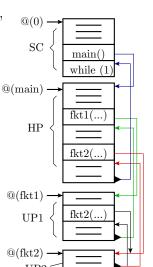

## Unterprogramme

#### 4. Unterprogramme

#### Unterprogramme

Unterprogramme sind Programmbausteine,

- die als Befehlsfolge vom Programmiergerät in den Befehlsspeicher (Flash) geschrieben und

- durch Aufruf ihrer Adresse in den Programmfluss anderer Programme eingefügt werden.

Programme eingefügt werden.

SC automatisch eingefügter Startcode

HP Hauptprogramm

UPi Unterprogramm i

@(0) Adresse 0, Startadresse Mikrorechner

nach Neuprogrammierung, Einschalten,

@(...) Startadresse Unterprogramm

Rücksprung

\*\*\*(...) Aufruf von \*\*\* mit den Parametern ...

while (1) Endlosschleife

andere Anweisungen

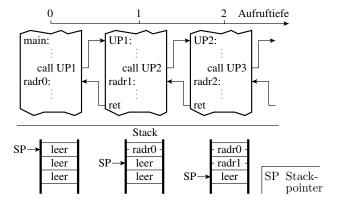

## 4. Unterprogramme

## Verwaltung der Rücksprungadressen

Die Rückkehradressen werden auf einem Stapelspeicher (Stack) nach dem Prinzip »First In Last Out« gespeichert und beim Rücksprung wieder entnommen. Nach diesem Prinzip können Unterprogramme selbst Unterprogramme verwenden.

## 4. Unterprogramme

### Befehle für die Arbeit mit Unterprogrammen

| Operation           | Т | OpCode              | Assembler |

|---------------------|---|---------------------|-----------|

| PC←PC+k+1,          | 3 | 1101 kkkk kkkk kkkk | rcall k   |

| STACK←PC+1, SP←SP-2 |   |                     |           |

| PC←0b00:Z,          | 4 | 1001 010 0000 1001  | icall k   |

| STACK←PC+2, SP←SP-3 |   |                     |           |

| PC←EIND:Z,          | 4 | 1001 010 0001 1001  | eicall    |

| STACK←PC+2, SP←SP-3 |   |                     |           |

| PC←k, STACK←PC+2,   | 5 | 1001 010k kkkk 111k | call k    |

| SP←SP-3             |   | kkkk kkkk kkkk kkkk |           |

| PC←STACK, SP←SP+3   | 5 | 1001 010 0000 1000  | ret       |

| STACK←Rr, SP←SP-1   | 2 | 1001 001d dddd 1111 | push Rd   |

| Rd←STACK, SP←SP+1   | 2 | 1001 000d dddd 1111 | pop Rr    |

push und pop dienen zur Zwischenablage von Registerinhalten auf dem Stack.

#### Stack einrichten

Der Stack ist ein Bereich des Datenspeichers, der vom Stackpointer adressiert wird. Der Stackpointer besteht aus den EA-Registern SPL und SPH auf den Adressen 0x3D und 0x3E. Auf dem Stack werden gespeichert:

- die Rücksprungadressen

- die mit push gesicherten Registerinhalte und

- die lokalen Variablen.

Der Stack muss vor dem ersten Unterprogrammaufruf, d.h. vor Aufruf von main() initialisiert werden. Unser Compiler initialisiert den Stack im Startup-Code mit der höchsten Adresse des internen RAMs 0x21FF:

```

00074 SER R28

00075 LDI R29,0x21

00076 OUT 0x3E,R29

00077 OUT 0x3D,R28

```

1. Lokale Variablen

### Lokale Variablen

#### Globale und lokale Variablen

#### Globale Variablen

- werden außerhalb der Unterprogramme vereinbart und

- haben feste Adressen.

#### Lokale Variablen

- werden innerhalb der Unterprogramme vereinbart und

- erhalten Adressen auf dem Stack<sup>5</sup> relativ zum Frame-Pointer.

```

uint8 t g1, g2;

11

Name

Value

Type Locals

□void main(void){

uint8 t{data}@0x21f8 ([R28]+1)

I1

0x83

13

uint8 t 11 = 0x83;

uint8_t{data}@0x21f9 ([R28]+2)

12

0x45

14

uint8 t 12 = 0x45;

13

0x7a | uint8 t{data}@0x21fa ([R28]+3)

15

uint8 t 13 = 0x7A;

Value Type Watch 1

Name

16

g1 = 11 + 12;

0xc8

uint8_t{data}@0x0200

q1

g2 = g1 + 13;

17

q2 0x42

uint8_t{data}@0x0201

Hier ist der Frame-Pointer Y gemeint.

```

<sup>&</sup>lt;sup>5</sup>Ab -O1 erhalten Variablen, wenn Platz ist, Registeradressen.

Füll-

Stack A

# 4. Unterprogramme

Im Beispielprozessor werden die Adressen für globale Variablen ab 0x200 aufsteigend vergeben. Der Stack beginnt am Speicherende und wird absteigend gefüllt. Die lokalen Variablen werden relativ zum Framepointer (Register Y) adressiert.

Beim Unterprogrammaufruf werden Rücksprungadresse und zu sichernde Register (ZR) auf den Stack gelegt. Dann wird für die lokalen Variablen Platz geschaffen und dem Framepointer der Wert des Stackpointers zugewiesen.

Beim Rücksprung zum aufrufenden Programm wird der Stack in umgekehrter Reihenfolge abgeräumt. Die lokalen Variablen sind danach ungültig.

richtung Y→ frei LV aktuel-ZRles UP RALVaufrufen-ZRdes UP -RA

LV lokale Variablen

ZR zu sichernde Register

RA Rückkehradresse zum aufrufenden Unterprogr.

RA\* Rückkehradresse zum Startup-Code

#### Beispielprogramm mit -O0

```

11

uint8 t g1, g2;

0008E

LDI R24,0x7A

15

12 ⊡void main(void){

0008F

STD Y+3,R24

13

uint8 t 11 = 0x83;

00090

LDD R25,Y+1

14

uint8 t 12 = 0x45;

00091 LDD R24,Y+2

15

uint8_t 13 = 0x7A;

ADD R24, R25

00092

g1 = 11 + 12;

16

STS 0x0200, R24

00093

g2 = g1 + 13;

17

00095

LDS R25,0x0200

00097

LDD R24,Y+3

00085

PUSH R28

00098

ADD R24, R25

PUSH R29

00086

STS 0x0201,R24

00099

00087 RCALL PC+0x0001 2

0009B

POP RØ

00088 IN R28,0x3D

0009C

POP RØ

00089 IN R29,0x3E

0009D

POP RØ

0008A LDI R24,0x83

0008B STD Y+1,R24 13

0009E

POP R29

0008C LDI R24,0x45

0009F

POP R28

0008D STD Y+2,R24

000A0

RET

```

| 00085 | PUSH R28                     | 0009B<br>0009C   | POP | RØ  |   |

|-------|------------------------------|------------------|-----|-----|---|

| 00086 | PUSH R28<br>PUSH R29         | 0009C            | POP | RØ  |   |

| 00087 | RCALL PC+0x0001              | 2 0009D<br>0009E | POP | RØ  | 4 |

| 00088 | IN R28,0x3D                  | 0009E            | POP | R29 |   |

| 00089 | IN R28,0x3D<br>IN R29,0x3E 3 | 0009F            | POP | R28 |   |

|       |                              | 000A0            | RET |     |   |

- 1 Sichern des Framepointers des aufrufenden Programms.

- Der reall-Befehl verringert den Stackpointer um 3. Das er dabei die Rückkehradresse 0x000088 auf den Stack schreibt, stört nicht, weil dieser Wert nie gelesen wird.

- Zuweisen des neuen Stackpointer-Wertes an den Framepointer. Danach haben die lokalen Variablen die Adressen:

| Variable | l1  | ls2 | l3  |

|----------|-----|-----|-----|

| Adresse  | Y+1 | Y+2 | Y+3 |

4 3×pop r0 erhöht den Stackpointer um 3. Dann wird der alte Framepointer-Wert zurückgeholt und zurückgesprungen.

## Gesicherte und zu sichernde Register

Außer dem Framepointer r29 und r28 müssen auch die anderen vom aufrufenden Programm genutzten Register vor Änderung durch das aufgerufene Programm auf dem Stack gesichert werden.

Für den gcc in AVR-Studio gilt für die Registernutzung:

- Von r1 wird erwartet, dass sein Wert immer null ist

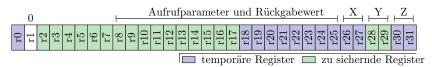

- r0, r18:27 (incl. X) und r30:31(Z): Temporäre Register, die von aufgerufenen Unterprogrammen verändert werden dürfen. (Sicherung durch aufrufendes Programm.)

- r2:17, r28:29 (Y): zu sichernde Register. Sie muss das aufgerufene Programm, falls es sie nutzt, auf dem Stack sichern.

Das folgende mit -O1 übersetzte Hauptprogramm legt die Variablen a, b und c in Registern an und optimiert die Variablen d und e weg.

```

Watch 1

10

uint8_t g;

□void main(void){

11

Name

Value

Type

12

uint8 t a = PINA;

a 0x00

uint8_t{registers}@R24

13

uint8 t b = PINB;

b 0x02

uint8_t{registers}@R18

14

uint8 t c = PINC;

c | 0x00

uint8_t{registers}@R25

15

uint8 t d = a + b;

d Optimized away

Error

16

uint8_t = a - c;

e Optimized away

Error

17

g = d \mid e

g 0x00

uint8 t{data}@0x0200

```

Die genutzten Register r24, r18 und r25 sind temporäre Register und müssen nicht gesichert werden.

Die Mehrheit der C-Anweisung werden in dem Beispiel direkt in einen Maschinenbefehl übersetzt.

```

uint8 t g;

10

Adresse: 0x200

∃void main(void){

uint8 t a = PINA; | 00085 IN R24,0x00

12

uint8 t b = PINB; | 00086 IN R18,0x03

13

uint8 t c = PINC; | 00087 IN R25,0x06

14

00088 MOV R19,R24

16

uint8_t e = a - c; | 00089 SUB R19, R25

15

uint8 t d = a + b; | 0008A ADD R24,R18

g = d | e;

0008B OR R24,R19

17

0008C STS 0x0200,R24

0008F

RFT

```

Mit dem zusätzlichen Aufruf eines Unterprogramms, das auch Register für seine lokalen Variablen verwendet, nimmt der Compiler statt der temporären Register r18, r24 und r25 die zu sichernden Register r17, r28 und r29:

```

□void main(void){

18

19

uint8 t a = PINA;

20

uint8 t b = PINB;

21

uint8 t c = PINC;

22

UP();

23

uint8_t d = a + b;

24

uint8 t e = a - c;

g = d \mid e;

25

26

```

| Watch 1 |   |                |                        |

|---------|---|----------------|------------------------|

| Name    | е | Value          | Туре                   |

| 9       | а | 0xff           | uint8_t{registers}@R28 |

| 9       | b | 0x21           | uint8_t{registers}@R29 |

| Ý       | С | 0x00           | uint8_t{registers}@R17 |

| 9       | d | Optimized away | Error                  |

| Ý       | е | Optimized away | Error                  |

| Q.      | g | 0x00           | uint8_t{data}@0x0200   |

| 9       | h | 0x00           | uint8_t{data}@0x0201   |

Diese werden am Anfang von main() auf den Stack gesichert und am Ende von main() wieder von Stack geholt.

```

18 ⊟void main(void){

10008B

PUSH R17

PUSH R28

10008C

10008D

PUSH R29

10008E

IN R28,0x00

19

uint8 t a = PINA;

10008F

IN R29,0x03

20

uint8 t b = PINB;

uint8_t c = PINC;

100090

IN R17,0x06

21

00091

RCALL PC-0x000C 22

UP();

00092

MOV R24, R28

24

uint8_t = a - c;

100093

SUB R24,R17

100094

ADD R28, R29

23

uint8 t d = a + b;

100095

OR R28, R24

g = d \mid e;

25

STS 0x0200, R28

100096

100098

POP R29

100099

POP R28

POP R17

10009A

26 }

```

- Register r17, r28 und r29 auf dem Stack sichern.

- 2 Register r17, r28 und r29 vom Stack holen.

Parameterübergabe

### Registernutzung und Parameterübergabe

temporäre Register 🖂 zu sichernde Register

- Von links beginnen werden die ersten 18 Aufrufparameterbytes in den Registern r25:8 und alle weiteren auf dem Stack übergeben. 1-Byte Parameter nutzen nur jedes zweite Byte.

- Die Rückgabe erfolgt in den Registern r25:8.

```

Į(j)

```

```

uint16_t UP(uint16_t a,

Name

Value

Type

13 ⊟

uint16 t b){

a

0x034a

uint16_t{registers}@ R25 R24

uint16 t c = a \ll 1;

14

uint16 t{registers}@ R23 R22

0x0127

uint16 t d = c \mid b;

15

C

Unknown locati Error

16

return d;

d

Unknown locati Error

17 }

```

Registerzuordnung der Übergabeparameter wie vorhergesagt.

```

uint16 t UP(uint16 t a,

Name

Value

Type

13 ⊟

uint16 t b){

Unknown locati Error

14

uint16 t c = a \langle\langle 1;

b

Unknown locati Error

15

uint16 t d = c \mid b;

C

0x0694

uint16_t{registers}@ R25 R24

return d;

16

0x07b7

uint16 t{registers}@ R23 R22

d

```

- Wenn a und b nicht mehr gebraucht werden, Neuvergabe der Register, im Beispiel an die Variablen c und d.

- Vor dem Rücksprung muss der Wert der Variablen d (r23:r22) in das Registerpaar r25:r24 kopiert werden.

```

4. Unterprogramme

```

```

0007D

LSL R24

uint16 t UP(uint16 t a,

ROL R25

0007E

uint16 t b){

0007F

OR R22, R24

14

uint16_t c = a << 1;

00080

OR R23, R25

uint16 t d = c \mid b;

00081

MOV R24, R22

16

return d;

00082

MOV R25, R23

00083

RET

d (r23:r22) auf den Rückgabeplatz

(r25:r24) kopieren

00084

LDI R22,0x27

00085

LDI R23,0x01

Übergabewerte für a und b schreiben

00086

LDI R24,0x4A

LDI R25,0x03

00087

19 □ int main(){

00088

RCALL PC-0x000B

20

uint16 t e=UP(0x34a, 0x127);

00089

MOVW R18, R24

21

return e + 4;

0008A

SUBI R18,0xFC

22

Subtraktion 0xFE=-4

SBCI R19,0xFF

0008B

MOV R24,R18

0008C

e (r19:r18) auf den Rückgabeplatz

0008D

MOV R25, R19

(r25:r24) kopieren

0008E

RFT

```

#### Rekursion

#### Rekursion

Ein rekursives Programm ruft sich so lange selbst auf, bis eine Abbruchbedingung erreicht ist. Beispiel für ein rekursiv beschreibarer Algorithmus ist die Berechnung der Fakultät:

$$n! = \begin{cases} n \cdot (n-1)! & n > 1\\ 1 & \text{sonst} \end{cases}$$

Ein rekursives Programm speichert bei jedem Aufruf von sich selbst die Rücksprungadresse und die zu sichernden Registerinhalte auf den Stack und reserviert Platz für die lokalen Variablen. Gute Demonstration einer tiefen Unterprogrammverschachtelung und einer intensiven Stack-Nutzung.

#### Rekursive Rechtsverschiebung

Die 4-Byte Variable a (r25, r24, r23, r22) wird bei jedem Aufruf halbiert und die Variable n (r20) um eins verringert:

|                 | Name | Value      | Туре                                 |

|-----------------|------|------------|--------------------------------------|

| 1. Aufruf       | 🕏 a  | 0x5f317e1a | uint32_t{registers}@ R25 R24 R23 R22 |

| 1. 1141141      | n    | 0x05       | uint8_t{registers}@R20               |

| 2. Aufruf       | a    | 0x2f98bf0d | uint32_t{registers}@ R25 R24 R23 R22 |

| <b>2.</b> 11ana | n    | 0x04       | uint8_t{registers}@R20               |

| •••             |      |            |                                      |

| 5. Aufruf       | a    | 0x05f317e1 | uint32_t{registers}@ R25 R24 R23 R22 |

| 0               | a n  | 0v01       | uint@ t(rogictore)@P20               |

#### Das Hauptprogramm

```

00092

LDI R20,0x05

Variable B mit 5 initialisieren

00093

LDI R22,0x1A

Variable a mit 0x5F317E1A

00095

LDI R24,0x31

initialisieren

00096

LDI R25,0x5F

initialisieren

00097

RJMP PC-0x001A

Sprung zum Unterprogramm.

```

■ Durch den Ansprung des Unterprogramms ist der Rücksprung vom Unterprogramm gleich der Rücksprung von main() zum Startup-Code (Adresse 0xB7).

#### Das Unterprogramm beginnt ab Adresse 0x7D:

```

00007DPUSH R16Registerinhalte von r16 und r1700007EPUSH R17auf den Stack ablegen.00007FMOVW R16,R22Die Werte der Aufrufvariablen a000080MOVW R18,R24in die Register r16 bis r19 kopieren.000081TST R20Test, ob Aufrufparameter b null ist. Wenn000082BREQ PC+0x09ja, springe zum Ende des Unterprogramms.

```

# 4. Unterprogramme

00091

RET

```

00083

LSR R25

Rechstverschiebung der 4

00084

ROR R24

Bytes der Variablen a.

00085

ROR R23

00086

ROR R22

b \leftarrow b+1

SUBI R20,0x01

00087

I Erneuter Aufruf von sich selbst.

00088

RCALL PC-0x000B

00089

MOVW R16, R22

Rückgabewert in r22 bis r25 in r16 bis r19 kopieren.

MOVW R18, R24

0008A

0008B

MOV R22, R16

r16 bis r19 zurück in r22 bis

MOV R23,R17

0008C

r25 kopieren (offenbar ohne Sinn).

MOV R24,R18

0008D

0008E

MOV R25, R19

Die auf den Stack abgelegten Inhalte

0008F

POP R17

zurück in r16 und r17 kopieren.

00090

POP R16

```

Rücksprung

Bei jedem Aufruf werden auf den Stack abgelegt:

- die Rücksprungadresse (17 Bit, 3 Bytes)

- die mit push abgelegten Registerinhalte von r16 und r17.

# Beim 5

Beim 5. Stopp am Unterbrechungspunkt liegen auf dem Stack:

- 21FD bis 21FF: Rücksprungadresse zum Startup-Code,

- 5×die Rücksprungadresse zu sich selbst und

- $6 \times$  die Registerinhalte von r16 und r17.

| data | 0x21E0 | 00 00 17 e1 |                                                 |

|------|--------|-------------|-------------------------------------------------|

| data | 0x21E4 | 00 00 89 2f |                                                 |

| data | 0x21E8 | c3 00 00 89 |                                                 |

| data | 0x21EC | 5f 86 00 00 | 00 00 7b Rücksprungadresse<br>zum Startup-Code  |

| data | 0x21F0 |             | 00 00 89 Rücksprungadresse<br>zum Unterprogramm |

| data | 0x21F4 | 00 89 7e 1a | zum Unterprogramm                               |

| data | 0x21F8 | 00 00 89 00 | Wert von r16                                    |

| data | 0x21FC | 00 00 7b    | Wert von r17                                    |

# Aufgaben

# Aufgabe 2.7: Übergaberegister

Das nachfolgende in einer Header-Datei vereinbarte Unterprogramm:

```

uint16 UP(uint8_t a, uint16_t b, uint8_t c);

```

soll in Assembler geschrieben werden. In welchen Registern bekommt das Assemblerprogramm die Operanden übergebenen und in welchen Registern muss der Rückgabewert stehen?

### Aufgabe 2.8: Multiplizierunterprogramm

Die nächste Folie zeigt ein Unterprogramm, das aus 16-Bit Faktoren ein 32-Bit Produkt bildet, ein Hauptprogramm, dass dieses mit Beispielzahlen aufruft und das mit -O1 übersetzte disassemblierte Programm. Das Programm verhält sich nicht wie erwartet.

- In welchen Registern werden die Faktoren übergeben und in welchen Registern erwartet das Hauptprogramm das Ergebnis?

- Bestimmen Sie auf der nächsten Folie die Werte, die nach jeder Anweisung in den Registern stehen und füllen Sie die Tabelle aus.

- Was ist bei der Berechnung falsch?

- Schreiben Sie ein Assemblerprogramm mit derselben Aufrufschnittstelle, das ein korrektes 4-Byte-Produkt berechnet und zurück gibt.

LDI R25,0x00

RFT

00088

00089

#### Aufgabe 2.9: Schleife mit Fehler

Das nachfolgende C-Programm enthält eine while-Schleife, in der die Variable a solange ihr Wert kleiner 256 ist um 1 erhöht wird. Dazu sind die disassemblierten mit O0 und mit O1 übersetzten Programme gezeigt.

```

C-Programm mit while-Schleife

Mit O0 compiliertes Programm

11 ⊡void main(void){

0007D

PUSH R28

0007E PUSH R29

12

uint8 t a;

13

while(a<256){

0007F PUSH R1

IN R28,0x3D

14

00080

a++;

00081

IN R29,0x3E

15

LDD R24,Y+1

16

00082

00083

SUBI R24,0xFF

Mit O1 compiliertes Programm

00084

STD Y+1,R24

0007D

RJMP PC-0x0000

RJMP PC-0x0003

00085

```

- Warum wird das Programm mit -O1 in eine Endlosschleife übersetzt, die nichts tut?

- Verhält sich das mit -O0 übersetzte Programm anders?

- Wie ist das C-Programm zu verändern, damit die Schleife abbricht, wenn a nicht mehr kleiner als 256 ist?

- Welchen Wert hat in dem mit -O0 übersetzten Programm der Stackpointer am Eintrittspunkt von main() (Halt vor Adresse 0x7D)?

- Welchen Wert hat in dem mit -O0 übersetzten Programm der Framepointer nach Abarbeitung der Anweisung auf Adresse 0x81?

Hinweis: Vor Aufruf von main() wird der Stackpointer mit 0x21FF initialisiert und eine Rücksprungadresse beansprucht 3 Bytes auf dem Stack.