# Einführung in die Elektronik Große Übung 3

G. Kemnitz, C. Giesemann

Institut für Informatik, Technische Universität Clausthal

2. Dezember 2015

## TU Clausthal

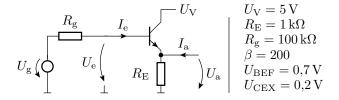

#### Aufgabe 3.1

#### Gesucht sind:

- Ersatzschaltung mit dem Transistor im Normalbetrieb.

- Übertragungsfunktionen:  $U_{\rm a} = f\left(U_{\rm e}\right)$  und  $U_{\rm a} = f\left(U_{\rm g}\right)$  für  $I_{\rm a} = 0$

- Spannungsbereich von  $U_{\rm e}$  und  $U_{\rm g}$ , in dem das Modell gültig ist.

- Eingangswiderstand  $R_{\rm e} = \frac{dU_{\rm g}}{dI_{\rm e}}$  für  $I_{\rm a} = 0$

- Ausgangswiderstand  $R_{\rm a} = \frac{d U_{\rm a}}{d I_{\rm a}}$

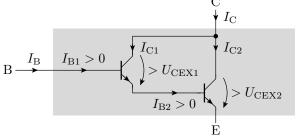

#### Aufgabe 3.2

Die Transistorschaltung in der nachfolgenden Abbildung wird als Darlington-Transistor bezeichnet.

- I Stellen Sie die lineare Ersatzschaltung für den Betriebsfall auf, dass beide Transistoren im Normalbetrieb arbeiten.

- 2 Vereinfachen Sie die lineare Ersatzschaltung soweit, dass sie nur noch aus einer Konstantspannungsquelle und einer stromgesteuerten Stromquelle besteht.

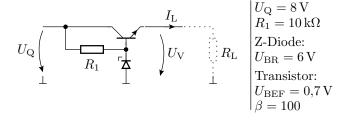

#### Aufgabe 3.3: Längsregler

Bestimmen Sie die linearen Ersatzschaltungen für die Arbeitsbereiche mit dem Transistor im Normalbetrieb und

- 1 der Z-Diode im Durchbruchbereich

- 2 der Z-Diode im Sperrbereich.

Wie verhält sich die Ausgangsspannung in Abhängigkeit vom Laststrom  $I_{\rm L}$  in den Bereichen, in den die Ausgangsspannung und der Laststrom > 0 sind?

#### Aufgabe 3.4: PWM

Für eine pulsbreitenmodulierte Leistungssteuerung mit einem NMOS-Transistor soll gelten:

- Versorgungsspannung:  $U_{\rm V} = 12 \, {\rm V}$

- Lastwiderstand:  $R_{\rm L} = 100 \, \Omega$

- $\blacksquare$  Periode des pulsbreitenmodulierten Signals:  $T_{\rm P}=100\,\mu{\rm s}$

- I Zeichnen Sie die Schaltung aus Schalttransistor und Lastwiderstand.

- 2 Bestimmen Sie die relative Pulsbreite  $\eta$ , die Ein- und die Ausschaltzeit bei dem der Leitungsumsatz  $P_{\rm RL}$  im Lastwiderstand im Mittel 0,2 W beträgt.

### Aufgabe 3.5: CMOS-Gatter

Entwickeln Sie je ein FCMOS-Gatter

11 mit der logischen Funktion:

$$y = \overline{(x_1 x_2) (x_3 \vee x_2)}$$

2 mit der logischen Funktion:

$$y = \bar{x}_1 \vee \bar{x}_2 \vee (\overline{x_1 \vee x_2 x_3} \wedge \bar{x}_3)$$

Hinweis: Versuchen Sie zuerst die Gleichungen soweit wie möglich zu vereinfachen.

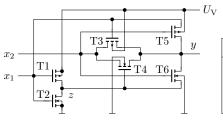

#### Aufgabe 3.6: Arbeitsbereiche

Bestimmen Sie in der nachfolgenden Transistorschaltung für alle logischen Eingabebelegungen von  $x_1$  und  $x_2$  in welchem Bereich jeder der sechs Transistoren arbeitet und den logischen Ausgabewert von y.

| $x_2$ | $x_1$ | z | T1 | T2 | T3 | T4 | T5 | T6 | y |

|-------|-------|---|----|----|----|----|----|----|---|

| 0     | 0     |   |    |    |    |    |    |    |   |

| 0     | 1     |   |    |    |    |    |    |    |   |

| 1     | 0     |   |    |    |    |    |    |    |   |

| 1     | 1     |   |    |    |    |    |    |    |   |

A aktiver Bereich S Sperrbereich  $\mathbf{S}^*$  Sperrbereich, wenn Paralleltransistor ein

Z hochohmig