# 1 Übungsblatt

### 1.1 Versuchsaufbau

Wie schon in Aufgabe 4 des Praktikums erwähnt wurde, ist die Fehlersuche ein nicht zu unterschätzender Bestandteil des Hardwareentwurfs. Als Vergleichsmöglichkeit zu Chipscope soll in dieser Aufgabe der externe Logikanalysator des Instituts angeschlossen und verwendet werden. Es handelt sich um einen Agilent 1671G Logik Analysator, der auf einem Rollwagen im Nebenlabor steht. Neben diesem benötigen Sie noch zwei Pinout-Adapter für die Durchführung dieser Aufgabe. Diese Übung unterteilt sich in zwei Teilaufgaben. In der ersten sollen Sie sich mit dem Logikanalysator vertraut machen und ihn erstmalig anschließen, in der zweiten Teilaufgabe wird eingehender auf die Verwendung des Analysators eingegangen, unter anderem verschiedene Triggerbedingungen, Aufzeichnungs- und Darstellungsmodi sowie Fehlererkennung.

## 1.2 Projekte vorbereiten

Legen Sie die neuen Verzeichnisse

H:\TGP\AufgabeLA1

und

H:\TGP\AufgabeLA2

an und kopieren Sie aus dem Netz die Dateien

- AufgabeLA1.npl

- AufgabeLA1.vhd

- AufgabeLA1.ucf

- AufgabeLA2.npl

- AufgabeLA2.vhd

- AufgabeLA2.ucf

in die entsprechenden neu angelegten Verzeichnisse.

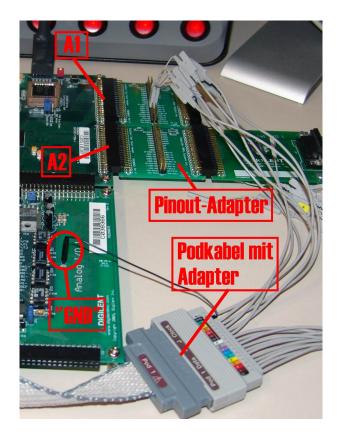

Abbildung 1: Darstellung der Kontaktstellen und verwendeten Pins

## 1.3 Logikanalysator anschließen

Der Logikanalysator hat an der Rückseite sechs Anschlusskabel gleicher Bauart, die mit den Bezeichnungnen POD1 bis POD6 beschriftet sind. Für die Versuchsdurchführung wird nur das mit POD1 beschriftete Kabel benötigt, da nie mehr als 15 Datenleitungen gleichzeitig verwendet werden. An dieses POD-Kabel wird nur ein Adapter angeschlossen, welches eine Aufteilung des Flachbandkabels in einzelne Datenleitungen mit integrierten Vorwiderständen vornimmt. Dieser Adapter ist wie das Anschlußkabel mit POD1 beschriftet und befindet sich in einer statischen Schutzhülle in einer Kiste unterhalb des Logikanalysators. Um die Datenleitungen nun anschließen zu können, müssen die Pinout-Adapter an das Entwicklungsboard angeschlossen werden. Als Hilfestellung für die Umbaumaßnahmen sei Abbildung 1 gegeben.

Dazu müssen die Erweiterungsboards (falls vorhanden) auf der Seite A der

Hauptplatine entfernt werden (normalerweise sind dies ein USB-Board und ein Board für den Anschluss der seriellen Schnittstelle). Dann werden die Pinout-Adapter angesteckt und die Erweiterungsplatinen wieder an die Adapter angeschlossen. Als nächstes müssen die Datenleitungen des Logikanalysators auf den Adapter gesteckt werden. Zuerst wird der mit "GND" beschriftete Stecker auf dem Analog-Zusatzboard auf den mit "GND" gekennzeichneten Pin gesteckt. Bei Aufgabenteil 1 verwenden Sie bitte den Adapter an dem A1-Port des Entwicklungsboards, bei Aufgabenteil 2 den Adapter an dem A2-Port mit folgender Zuordnung.

```

Anschlüsse für Aufgabenteil 1

Anschlüsse für Aufgabenteil 2

M-DB1

LAclkport

CLK \longleftrightarrow

M-DB4

1 \longleftrightarrow

M-DB2

LAdataport(0)

1 \longleftrightarrow

M-DB1

M-DB3

LAdataport(1)

M-DB4

LAdataport(2)

M-DB5

LAdataport(3)

M-DB6

LAdataport(4)

```

## 1.4 Aufgabenstellung für die erste Übungsaufgabe

In der ersten Übungsaufgabe soll ein grundlegendes Verständnis für die Vorbereitung zur Verwendung des Logikanalysators entstehen. Als Grundlage hierfür dient ein VHDL-Programm, welches ungefähr im Sekundentakt den btncode des Tasterfeldes abfragt und diesen auf den LEDs ausgibt. Die einzelnen Ziele dieser Aufgabe bestehen darin,

- den Logikanalysator anzuschließen,

- den Pinout bereitzustellen,

- den Logikanalysator einzurichten und

- erste Funktionstests durchzuführen.

Starten Sie zunächst das Projekt AufgabeLA1.

### 1.4.1 Anschluss des Logikanalysators

Verbinden Sie die Stecker von POD 1 mit den Anschlüssen des Pinout-Adapters an der Kontaktleiste A1 des Entwicklungsboards gemäß der Tabelle auf Seite 3. Auch der "GND"-Stecker muss verbunden werden.

### 1.4.2 Verbinden der Kontaktstellen mit dem Design

Wie schon in dem Tutorial des Praktikums müssen als erstes die Schaltkreisanschlüsse den Ports in dem Design zugewiesen werden. Dazu unter "User Constrains, Assign Package Pins" den PACE-Editor starten. Es erscheint das bekannte Bild, unter anderem auf der linken unteren Seite die bisher implementierten (zugewiesenen und nicht zugewiesenen) Ports. Zur besseren Übersicht unten auf Package View umschalten, dort werden die Anschlusspins des FPGA in grafisch ansprechenderer Weise dargestellt als in der Standarddarstellung. Als nächstes öffnen Sie die der Aufgabenstellung beigefügte grafische Darstellung der Anschlüsse des FPGAs (DesignFPGA.pdf). In den Darstellungen "I/O-Bank 1" und "I/O-Bank 2" auf Seite 3 finden Sie die für die Aufgaben benötigten Anschlüsse. Auf der linken Seite der gezeigten Anschlussleitungen stehen die Belegungen innerhalb des FPGA, die auch in PACE verbunden werden müssen. Die Bezeichnung auf der rechten Seite setzt sich folgendermaßen zusammen: XY-Z, wobei X einen Kennbuchstaben angibt, Y den Anschlussport (zum Beispiel A1 oder C2) und Z die Kennung des einzelnen Pins widerspiegelt. Auf den Pinoutadaptern finden sich dieselben Bezeichnungen wieder, nur ohne Bezug auf die entsprechenden Ports. Vergleichen Sie oben gezeigte Tabelle mit den Diagrammen und schreiben Sie sich die verwendeten FPGA-Pins auf. Tragen Sie diese in der Tabelle in PACE entsprechend der oben aufgeführten Zuordnung ein. Kompilieren Sie das Programm und übertragen Sie es auf den Mikroprozessor, nachdem Sie sichergestellt haben, dass der Schalter sw(1) auf "0" steht.

#### 1.4.3 Einrichten des Logikanalysators

Schalten Sie den Logikanalysator ein. Nachdem er hochgefahren ist, zeigt er im Startbild das Konfigurationsmenü für den Analysator. Mit der angeschlossenen Maus kann im oberen linken Menüpunkt "Analyser" der Menüeintrag "System" gewählt werden. Danach muss mittels Klick auf "external I/O" die Einstellung geändert werden auf "Harddisk". Nun mit dem am Analyser angebauten Drehrad auf das Unterverzeichnis "SWP" scrollen. Als nächstes

mit der Maus "Change Dir" anklicken. Wieder mit dem Scrollrad die Datei "Prakt.\_\_" auswählen und anschließend, wenn die Option "Load All" aktiviert ist, auf den "Execute"-Button klicken. Der Analysator lädt nun vorgefertigte Konfigurationsdateien, die die passenden Einstellungen für den ersten Versuch beinhalten. Wenn dies abgeschlossen ist, per Maus wieder umstellen von "System" auf "Analyser" und in dem auf "Configuration" stehenden Menü umschalten auf "Listing Machine 1". Hiernach nur noch den "Run"-Knopf auf der rechten Seite des Bedienteils drücken. Der Logikanalysator befindet sich nun in einem aufzeichnungsbereiten Zustand. Während des Betriebs können kurzzeitig grüne Warnhinweise im oberen Drittel des Bildschirms des Logikanalysators erscheinen. Diese weisen nur auf einen langsamen Takt hin, der in diesem Beispiel tatsächlich vorhanden ist, normalerweise aber auf eine Störung hinweisen würde.

#### 1.4.4 Test

Führen Sie ein paar Tests durch, indem Sie die Taster des Tastenfeldes drücken und den Schalter sw(1) auf "1" stellen. Was passiert? Wann beginnt der Logikanalysator mit der Aufzeichnung, wann stoppt er? Was zeichnet der Logikanalysator auf? Stoppen Sie hierfür die Aufzeichnung mittels der "Stop"-Taste am Logikanalysator und vergleichen Sie das erscheinende Listing mit den von Ihnen eingegebenen Werten über das Tastenfeld. Vergleichen Sie weiterhin die Anzahl der aufgezeichneten Werte mit dem Zählerwert auf dem Board. Durch die Einträge im Logikanalysator können Sie mit Hilfe des Scrollrades navigieren.

#### 1.4.5 Aufräumen

- Schalten Sie den Logikanalysator aus.

- Lösen Sie die Steckverbindung des Logikanalysators von dem Pinoutboard bis auf den "GND"-Anschluss.

- Löschen Sie unter dem Menüpunkt "Project, Cleanup Project Files" automatisch generierte Design-Files.

## 1.5 Aufgabenstellung für die zweite Übungsaufgabe

In der zweiten Übungsaufgabe wird näher auf die Konfigurations- und Funktionsaspekte des Logikanalysators eingegangen. Als Grundlage hierfür dient das VHDL-Programm der Aufgabe 9: "Serielle Schnittstelle". Die Übertragung vom PC zum Entwicklungsboard soll über den Logikanalysator mitgeschrieben und ausgewertet werden. Des Weiteren wurde das Programm so verändert, dass man über die Schalter sw(4)-sw(8) die Baudrate des Empfangsautomaten schrittweise binärcodiert verlängern kann. Die einzelnen Ziele dieser Aufgabe bestehen darin,

- den Logikanalysator anzuschließen,

- den Logikanalysator einzurichten,

- eine angemessene Triggerbedingung im Logikanalysator zu erstellen, um mit der Datenaufzeichnung zu beginnen,

- den "Fehler" in dem Originaldesign der Aufgabe 9 mittels des Logikanalysators zu finden und

- die Konsequenzen eines falschen Abtasttaktes im Empfangsautomaten zu ermitteln.

Starten Sie zunächst das Projekt AufgabeLA2, kompilieren Sie es und übertragen Sie die Bitdatei auf den FPGA.

### 1.5.1 Anschluss des Logikanalysators

Verbinden Sie die Stecker von POD 1 mit den Anschlüssen des Pinout-Adapters an der Kontaktleiste A2 des Entwicklungsboards gemäß der Tabelle auf Seite 3. Auch der "GND"-Stecker muss wieder verbunden werden.

## 1.5.2 Einrichten des Logikanalysators

Starten Sie den Logikanalysator und warten Sie bis der "Analyser, Configuration"-Bildschirm angezeigt wird. Wenn Sie den Anschluss von POD 1 korrekt vorgenommen haben, sollte in der Bildschirmmitte auf der linken Seite bei A1 ein \_ durch einen – ersetzt (nämlich der bei Bit 1) und

| _          | Low-Pegel         |

|------------|-------------------|

| _          | High-Pegel        |

| $\uparrow$ | wechselnder Pegel |

Abbildung 2: Zuordnungstabelle

neben dem J ein \(\frac{1}{2}\) zu erkennen sein. Klicken Sie nun auf "Timing" und ändern Sie die Einstellung auf "State". Damit ändern Sie die Aufnahmebedingung des Analysators von zeitlich konstanter zu einer änderungsbedingten Abtastung.

Klicken Sie als nächstes auf "Configuration" und wechseln Sie zum "Format"-Menü. In diesem Bildschirm können Sie auswählen, welche Leitungen der angeschlossenen Pods aufgezeichnet werden sollen. Da die serielle Schnittstelle nur über eine Leitung Daten empfängt, reicht es, bei Bus 1 das erste Bit zu aktivieren. Dies geschieht, indem Sie auf das entsprechende Feld klicken und in dem erscheinenden Dialog das erste Bit mit einem Sternsymbol (Aufzeichnung aktivieren) markieren, während alle anderen Bits bei der Einstellung "" verbleiben.

Als nächstes wechseln Sie vom "Format"-Menü in die "Trigger"-Einstellung. Hier wird die Konfiguration des Triggers vorgenommen, der die eigentliche Aufzeichnung startet. Dazu steht eine Auswahl an Triggerbedingungen zur Verfügung, die in einer Art Ablaufplan miteinander kombiniert werden können. Als erstes sollen Sie eine Triggerbedingung erstellen, die auf das ASCII-Zeichen "0" wartet und dann solange aufzeichnet, bis kein weiteres, direkt folgendes Zeichen gesendet wird. Dazu klicken Sie auf die "1", dann "Select Function". Mit dem Scrollrad auf "Find n-bit Pattern" und per Mausklick auswählen. In dem erscheinenden Konfigurationsbildschirm sicherstellen, dass ein 8-bit Pattern gesucht wird, und in dem entsprechenden Wert den Binärwert "00110000" einstellen. Als nächstes im Hauptbildschirm auf die "2" klicken, dann auf "Insert Level, Before". Hier die Funktion "Find event n consecutive times" auswählen. Im folgenden Konfigurationsbildschirm "8 x a" einstellen und bestätigen. Als letztes Klick auf "3" und "any state" in "no state" ändern und nach Bestätigung links unten mit dem Scrollrad auf das Symbol "a" und als Wert hierzu das "x" durch eine "1" ersetzen. Damit ist die Triggerbedingung fertig. Sie sucht in dem eingehenden Datenstrom nach dem ASCII-Zeichen "0", zeichnet dann alles auf, bis achtmal hintereinander die 1

kommt (was darauf hindeutet, dass kein weiteres Zeichen kommt) und hört dann mit der Aufzeichnung auf.

#### 1.5.3 Test

Testen Sie die Einstellung des Logikanalysators mit Hilfe von Hyperterminal. Senden Sie einzelne Zeichen an das Entwicklungsboard, nachdem Sie den Logikanalysator mittels des "Run"-Knopfes in den Wartezustand gebracht haben. Überprüfen Sie, ob wirklich nur Nullen aufgezeichnet werden und ändern Sie den eingetragenen Wert, um andere Zeichen zu erkennen. Als nächstes senden Sie eine Zeichenkette über Hyperterminal. Dazu öffnen Sie den Texteditor, geben dort eine Zeichenkette ein, kopieren diese und fügen Sie sie über "Bearbeiten, Einfügen" ein (die STRG-V Tastenkombination funktioniert leider nicht). Senden Sie Zeichenketten mit unterschiedlicher Länge. Überprüfen Sie die im Logikanalysator aufgezeichneten Werte mit denen auf dem Entwicklungsboard. Warum werden manchmal auf den LEDs falsche Werte angezeigt? Beheben Sie den Fehler im VHDL-Design, der sich im Zustandsautomaten befindet. Vergleichen Sie hierzu die vom Logikanalysator aufgezeichneten Werte mit dem Ablauf innerhalb des Automaten.

## 1.6 Zusatzaufgabe

In das VHDL-Design des Empfängers ist eine zuschaltbare Verzögerung des Handshake-Taktes implementiert. Diese kann über die Schalter sw(5) bis sw(8) in Binärschritten verändert werden und wird auf den LEDs 9-12 angezeigt. Dadurch kann die Auswirkung eines unsauberen Handshakes verdeutlicht werden. Der Logikanalysator läuft aber weiterhin mit dem richtigen Takt, damit die korrekten Werte zumindestens dort angezeigt werden und als Referenz verwendet werden können.

#### 1.6.1 Einrichten des Analysators

Zumal für diese Aufgabe nicht mehr nach einem bestimmten Zeichen gesucht werden muss, kann die Triggerbedingung vereinfacht werden. Gehen Sie in das Triggermenü und ändern Sie die erste Bedingung dahingehend, dass das erste Auftauchen eines niedrigen Pegels zum Start der Aufzeichnung führt.

### 1.6.2 Test

Senden Sie nun einzelne Zeichen als auch Zeichenketten über Hyperterminal, verändern Sie die Einstellung des Handshake-Taktes und vergleichen Sie die angezeigten Zeichen mit den aufgezeichneten des Logikanalysators. Ab welcher zeitlichen Verschiebung ergeben sich Abtastfehler?

## 1.6.3 Aufräumen

- Unter dem Menüpunkt "Project, Cleanup Project Files" automatisch generierte Design-Files löschen.

- Stromversorgung des FPGA ausschalten

- Modelsim und Projektnavigator beenden