# Aufgabe 2: Entwurf, Simulation und Test einer kombinatorischen Schaltung

Prof. G. Kemnitz, TU Clausthal, Institut für Informatik 28. April 2010

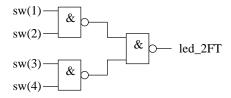

Das Schaltungsbeispiel besteht aus 3 NAND-Gattern:

Die Eingabe wird von den Schaltern SW1 bis SW4 auf dem DIO5-Board geliefert. Die Ausgabe erfolgt auf die Leuchtdiode LD1 auf der Hauptplatine.

# Projekt vorbereiten

Legen Sie ein neues Verzeichnis

H:/TGP/Aufgabe1

an und kopieren Sie die Design-Files aus dem Netz in dieses Verzeichnis:

Aufgabe1.vhd Strukturbeschreibung der Schaltung

my nand.vhd Funktionsbeschreibung der einzelnen Strukturbausteine

tgp.ucf Constrain-Datei der Versuchsbaugruppe

Anschließend erzeugen Sie ein neues Projekt ("File", "New Projekt"mit den Eigenschaften:

- Menue "Enter Name and Location ..."

- Project Name: Aufgabe1

- Project Location: H:/TGP/Aufgabe1

- Top-Level Module Type: HDL

- Menue "Select the Device ..."

- Device Famile: Spartan2e

- Device: xc2s300e

- Pachage: ft256

- Synthesis Tool: XST

- Simulator: ISim

- Generated Simulation Language: VHDL

- Menue "Create a New Source" übergehen

- Menue "Add Existing Source"

- Aufgabe1.vhd und my nand.vhd als VHDL-Module einbinden

- Praktikum.ucf als ucf-Datei zu Aufgabe1.vhd

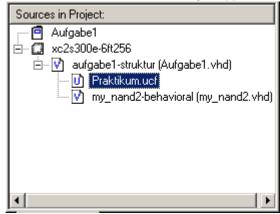

Ihr Source-Fenster wird, wenn alles geklappt hat, folgenden Baum angezeigt.

## Quelldatein ansehen

Doppel-Click auf eine VHDL-Datei öffnet diese im Editier-Fenster. Die ucf-Datei ist mit "Edit Constrains as Text" zu öffnen. Aufgabe1.vhd ist eine Strukturbeschreibung der Schaltung mit den 3 NAND-Gattern, my\_nand2.vhd die Beschreibung eines NAND-Gatters. In der ucf-Datei stehen außer für die 5 benötigten Schaltkreisanschlüsse die Pinzuordnungen für weitere Schaltkreisanschlüsse.

## Optionen einstellen

Damit die überflüssigen Einträge aus der ucf-Datei nicht auskommentiert werden müssen, ist wie im Tutorial unter "Implement Design, rechte Mouse-Taste, Properties, Translate Properties" das Flag "Allow Unmatched LOC Constrains" zu setzen. Gleichfalls ist unter "Generate Programming File, rechte Mouse-Taste, Properties, Startup Options" das Attribut "FPGA Start-Up Clock" in "JTAG Clock" umzuändern.

### Übersetzen und Testen

- Doppel-Click auf "Generate Programming File" und hoffen, das keine Fehlermeldung auftritt.

- Doppel-Click auf Configure Device (iMPACT) und weiter wie im ersten Tutorial.

- Nach erfolgreichem Down-Load kann die Leuchtdiode LD1 mit den Schaltern sw1 bis sw4 ein und ausgeschaltet werden. Testen Sie alle Variationen der Schalterstellungen durch, tragen Sie die Ergebnisse in eine Tabelle ein und vergleichen Sie das Ergebnis mit dem Sollverhalten:

| sw4 | sw3 | sw2 | sw1 | LD1 |

|-----|-----|-----|-----|-----|

| 0   | 0   | 0   | 1   | ?   |

| 0   | 0   | 1   | 0   | ?   |

|     |     |     |     |     |

#### Simulation

Die Simulation berechnet für vorgegebene Eingabesignale die Ausgabe. Dazu ist ein Testrahmen zu schreiben (siehe Vorlesung), z.B.:

```

library ieee;

use ieee.std_logic_1164.all;

use work.Aufgabe1;

entity TB is end entity;

architecture Beschreibung of TB is

signal sw : std_logic_vector(4 downto 1);

signal led: std_logic;

begin

Testobjekt: entity Aufgabe1(Struktur) port map(sw => sw, led_2FT => led);

process

wait for 50 ns; sw <= "1001";

wait for 50 ns; sw <= "1101";

...

wait;

end process;

end architecture;</pre>

```

Zum Start der Simulation

- In dem Auswahlmenü »Sources for« über dem Hierarchiefenster ist »Behavioral Simulation« auszuwählen

- Im Fenster »Hierarchie« den Testrahmen »TB« auswählen

- Im Fenster »Processes for TB(Beschreibung) « zuerst »Behavioral Check Syntax « auswählen « und möglicherweise vorhandenen Fehler beseitigen

- Wenn der Syntaxtest erfolgreich durchläuft, »Simulate Behavioral Model« auswählen.

- Im aufgenden Simulatorfenster Zoom richtig einstellen etc.

## Zusatzaufgabe

Modifizieren Sie die Beispielschaltung und wiederholen Sie die einzelnen Arbeitsschritte. In der Datei » Praktikum.ucf« finden Sie dazu die Namen der anderen Leuchtdioden, Schalter und Taster.

#### Aufräumen

• Über Menuepunkt "Project, Cleanup Project Files" automatisch generierte Design-Files löschen.